#### ANGLIA RUSKIN UNIVERSITY

#### FACULTY OF SCIENCE AND TECHNOLOGY

#### CONCEPTUAL DEVELOPMENT OF A NOVEL DIGITAL CONTROLLER FOR OPTIMISED OPERATION OF A HYBRID RENEWABLE ENERGY SYSTEM

#### JOHN DARVILL

A thesis in partial fulfilment of the requirements of Anglia Ruskin University for the degree of Doctor of Philosophy

Submitted January 2018

# Acknowledgements

I would like to express my deep gratitude to my supervisor, Dr Alin Tisan, for his consistent support and guidance over the last five years. I would also like to offer my thanks to my second supervisor, Professor Marcian Cirstea, not only for his support during my PhD but also for inspiring me during my undergraduate degree and sparking my interest in this topic. This project would not have been possible without the invaluable input you both offered.

#### ANGLIA RUSKIN UNIVERSITY

#### ABSTRACT

#### FACULTY OF SCIENCE AND TECHNOLOGY

#### CONCEPTUAL DEVELOPMENT OF A NOVEL DIGITAL CONTROLLER FOR OPTIMISED OPERATION OF A HYBRID RENEWABLE ENERGY SYSTEM

#### JOHN DARVILL

#### January 2018

The popularity of renewable energy has increased dramatically in the last decade as it becomes increasingly apparent that an alternative to fossil fuel is required. In order for this market to continue to grow, there are a number of technical issues which must be overcome. One such issue is the instability of power supplies which rely on unpredictable natural resources. A popular solution to this problem is the use of a number of complementary renewable power sources to create a stable power network serving a small geographical area. In this project, a novel control solution for such a system is proposed and modelled using a new approach.

A comprehensive review of the existing research literature was used to place in context the hybrid renewable energy concept. This included identification of a system topology as well as the novel control solution. A model of the system has been developed using a combination of PSim and MATLAB. This model allowed for the operation of the system to be simulated and subsequently verified. Upon completion of successful system level simulation testing, VHDL implementations of the control solution were created and incorporated into the model. Further simulations were then carried out based on a specific hardware target, an All Programmable System-on-Chip (APSOC) device featuring a dual-core CPU and an FPGA fabric.

The novel control solution is primarily aimed at the optimal control of the system's power converters. This controller employs a Neuro-Fuzzy algorithm to provide gain scheduling for a PI type controller. The test results indicate that improvements were achieved in the stability of the power converters in comparison to more traditional approaches, offering improved response times and a reduction of the output voltage error. Moreover, a state-based algorithm is utilised, which was demonstrated to ensure that the renewable energy sources are optimally complementary.

# **Table of Contents**

| 1  | Intro  | oduc   | tion                                                           | 1        |

|----|--------|--------|----------------------------------------------------------------|----------|

|    | 1.1    | Res    | earch Objectives                                               | 1        |

|    | 1.2    | Met    | hodology                                                       | 2        |

|    | 1.3    | Orig   | jinal Contributions                                            | 3        |

|    | 1.4    | Stru   | cture of the Thesis                                            | 3        |

| 2  | Rev    | view   | of Existing Renewable Power System Technologies and Advanced F | lesearch |

| Tı | ends . |        |                                                                | 5        |

|    | 2.1    | Rer    | newable Energy Sources and Technologies Employed               | 9        |

|    | 2.1.   | 1      | Wind Systems                                                   | 9        |

|    | 2.1.   | 2      | PV Systems                                                     |          |

|    | 2.1.   | 3      | Fuel Cells                                                     |          |

|    | 2.1.   | 4      | Other Sources                                                  | 14       |

|    | 2.2    | Mai    | n Power Converter Topologies used in Renewable Applications    | 14       |

|    | 2.2.   | 1      | History of Power Converters                                    |          |

|    | 2.2.   | 2      | Rectifiers                                                     |          |

|    | 2.2.   | 3      | Inverters                                                      |          |

|    | 2.2.   | 4      | AC to AC Converters                                            |          |

|    | 2.2.   | 5      | DC to DC Converters                                            | 21       |

|    | 2.3    | Мос    | dern Trends in Wind and PV Systems                             |          |

| 3  | Rev    | view   | of Control Technologies and Advanced Research Trends           |          |

|    | 3.1    | Cor    | trol Systems for Power Converters                              |          |

|    | 3.1.   | 1      | Control Principles and Traditional Systems                     |          |

|    | 3.1.   | 2      | PID Control                                                    |          |

|    | 3.1.   | 3      | Intelligent Controllers                                        |          |

|    | 3.2    | AI-E   | Based Controllers for Integrated Renewable Systems             |          |

|    | 3.2.   | 1      | Fuzzy Control                                                  |          |

|    | 3.2.   | 2      | Neural Networks                                                |          |

|    | 3.2.   | 3      | Neuro-Fuzzy Control                                            |          |

|    | 3.2.   | 4      | Evolutionary Algorithms in Control                             |          |

| 4  | Мос    | dellin | g and Hardware Tools                                           |          |

|    | 4.1    | Rev    | iew of Modelling Tools                                         |          |

|    | 4.1.   | 1      | Matlab                                                         |          |

|    | 4.1.   | 2      | SystemC and Handel-C                                           |          |

|    | 4.1.   | 3      | VHDL and Verilog                                               |          |

|   | 4.1.4 |        | VHDL-AMS and System Verilog                                                 | 51   |

|---|-------|--------|-----------------------------------------------------------------------------|------|

|   | 4.1.  | 5      | PSim                                                                        | 52   |

|   | 4.2   | Pote   | ential Hardware Solutions                                                   | . 53 |

|   | 4.2.  | 1      | Microprocessors and DSPs                                                    | . 53 |

|   | 4.2.  | 2      | FPGAs                                                                       | . 54 |

|   | 4.2.  | 3      | ASIC                                                                        | . 55 |

|   | 4.2.  | 4      | All Programmable System-on-Chip (APSOC)                                     | . 56 |

|   | 4.3   | Met    | hodology and Tools Used in this Project                                     | . 57 |

| 5 | Мос   | lellin | g of Local Renewable Power Converters                                       | 61   |

|   | 5.1   | Pho    | tovoltaic Power Converter                                                   | 63   |

|   | 5.1.  | 1      | Topology                                                                    | 63   |

|   | 5.1.  | 2      | Modelling                                                                   | 65   |

|   | 5.1.  | 3      | Simulations                                                                 | 77   |

|   | 5.2   | Win    | d Power Converter                                                           | 82   |

|   | 5.2.  | 1      | Topology                                                                    | 82   |

|   | 5.2.  | 2      | Modelling                                                                   | 82   |

|   | 5.2.  | 3      | Simulation                                                                  | 84   |

|   | 5.3   | Sup    | er Capacitor Power Converter                                                | . 87 |

|   | 5.3.  | 1      | Topology                                                                    | . 87 |

|   | 5.3.  | 2      | Modelling                                                                   | . 89 |

|   | 5.3.  | 3      | Simulation                                                                  | . 91 |

|   | 5.4   | Batt   | ery Power Converter                                                         | . 95 |

|   | 5.4.  | 1      | Topology                                                                    | . 96 |

|   | 5.4.  | 2      | Modelling                                                                   | . 98 |

|   | 5.4.  | 3      | Simulation                                                                  | . 99 |

|   | 5.5   | Con    | clusions                                                                    | 102  |

| 6 | Мос   | lellin | g of the Power Controller                                                   | 104  |

|   | 6.1   | Ope    | eration and Modelling                                                       | 104  |

|   | 6.1.  | 1      | Switch Topologies                                                           | 107  |

|   | 6.2   | Syst   | tem Simulations                                                             | 110  |

|   | 6.2.  | 1      | Complementation of the Renewable Energy Sources                             | 110  |

|   | 6.2.  | 2      | Super Capacitor Simulations                                                 | 124  |

|   | 6.2.  | 3      | Battery Simulations                                                         | 126  |

|   | 6.3   | Con    | clusions                                                                    | 132  |

| 7 | Des   | ign c  | of the Novel Power Converter Controller for Digital Hardware Implementation | 134  |

|   | 7.1   | CPL    | J Functionality                                                             | 134  |

|   | 7.2                                                                  | FPG                                            | A Design                                               | 135 |  |  |

|---|----------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|-----|--|--|

|   | 7.2.                                                                 | 1                                              | ANFIS Algorithm Architecture                           | 136 |  |  |

|   | 7.2.                                                                 | 2                                              | PWM Generator                                          | 145 |  |  |

|   | 7.2.                                                                 | 3                                              | PI Controller                                          | 150 |  |  |

|   | 7.3                                                                  | Inter                                          | r-core Communication                                   | 151 |  |  |

|   | 7.3.                                                                 | 1                                              | AXI Control Registers                                  | 151 |  |  |

|   | 7.3.                                                                 | 2                                              | DMA Data Transfer                                      | 154 |  |  |

|   | 7.4                                                                  | Timi                                           | ng and Utilisation Analysis                            | 157 |  |  |

|   | 7.5                                                                  | Con                                            | clusions                                               | 158 |  |  |

| 8 | Pov                                                                  | ver C                                          | onverter Circuit Design and Experimental Testing       | 159 |  |  |

|   | 8.1                                                                  | Inter                                          | face Circuit Design                                    | 159 |  |  |

|   | 8.2                                                                  | Valio                                          | dation through Simulation                              | 163 |  |  |

|   | 8.3                                                                  | Exp                                            | erimental Testing                                      | 172 |  |  |

|   | 8.3.                                                                 | 1                                              | PWM Testing                                            | 172 |  |  |

|   | 8.3.                                                                 | 2                                              | ANFIS HW Testing                                       | 173 |  |  |

|   | 8.4                                                                  | Con                                            | clusions                                               | 175 |  |  |

| 9 | Cor                                                                  | nclusi                                         | ons                                                    | 177 |  |  |

|   | 9.1                                                                  | Sum                                            | mary of Achievements                                   | 177 |  |  |

|   | 9.2                                                                  | Con                                            | tributions to Knowledge                                | 178 |  |  |

|   | 9.3                                                                  | Furt                                           | her Work                                               | 179 |  |  |

|   | 9.3.                                                                 | 1                                              | System Enhancements                                    | 179 |  |  |

|   | 9.3.                                                                 | 2                                              | Areas of Further Investigation                         | 180 |  |  |

| R | eferen                                                               | ces                                            |                                                        | 182 |  |  |

| A | ppendi                                                               | x A –                                          | PSO Algorithm Script for Matlab                        | 197 |  |  |

| A | ppendi                                                               | x B –                                          | Psim Schematics for the Hybrid Renewable Energy System | 202 |  |  |

| A | Appendix C – C Code used in the Hybrid Renewable Energy System Model |                                                |                                                        | 212 |  |  |

| A | Appendix D – FPGA Design Files                                       |                                                |                                                        |     |  |  |

| A | Appendix E – C Code Used in the CPU Core                             |                                                |                                                        |     |  |  |

| A | ppendi                                                               | ppendix F – APSOC ANFIS Algorithm Test Results |                                                        |     |  |  |

| A | ppendix G – Published Materials                                      |                                                |                                                        |     |  |  |

# List of Figures

| Fig 1 Annual Growth Rates of Electricity Production from 1990 to 2016 in OECD Countries  | s    |

|------------------------------------------------------------------------------------------|------|

| (International Energy Agency (2017))                                                     |      |

| Fig 2 Shares in OECD Renewable Electricity Production for 2016 (International Energy     |      |

| Agency (2017))                                                                           | 6    |

| Fig 3 Solar PV Manufacturing by Country (SPV Market Research (2014 cited by Internatio   | onal |

| Energy Agency (2014)))                                                                   |      |

| Fig 4 Global Cumulative Growth of Wind Power Capacity (International Energy Agency       |      |

| (2013))                                                                                  | 7    |

| Fig 5 Capacity Factor History of Selected Wind Turbines (Wiser and Bolinger (2013))      | 7    |

| Fig 6 Forecast Growth in Geothermal Power Production by Region (International Energy     |      |

| Agency (2011))                                                                           | 8    |

| Fig 7 Wind turbine block diagram                                                         | 9    |

| Fig 8 Solar cell equivalent circuit                                                      | . 12 |

| Fig 9 Hydrogen fuel cell structure                                                       | . 13 |

| Fig 10 Fuel Cell Equivalent Circuit                                                      | . 13 |

| Fig 11 Traditional linear supply                                                         |      |

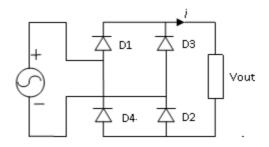

| Fig 12 Single phase full bridge rectifier                                                | . 16 |

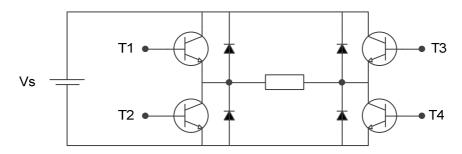

| Fig 13 Full Bridge Inverter                                                              | . 17 |

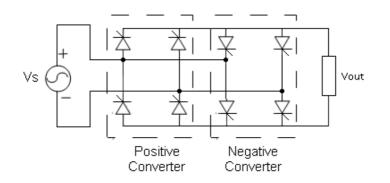

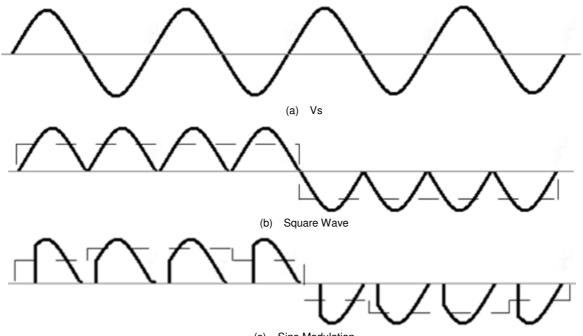

| Fig 14 Single phase to single phase cycloconverter                                       | . 19 |

| Fig 15 Single phase cycloconverter waveforms                                             | . 19 |

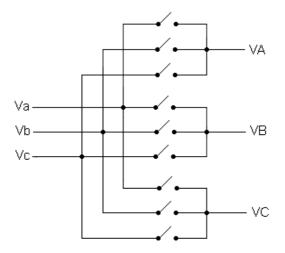

| Fig 16 Three-Phase Matrix Converter                                                      | . 20 |

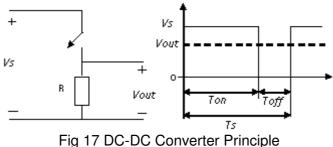

| Fig 17 DC-DC Converter Principle                                                         | . 21 |

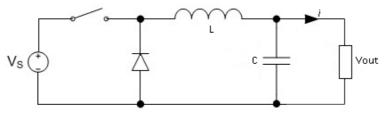

| Fig 18 Buck converter topology                                                           | . 22 |

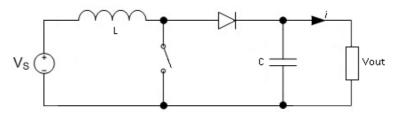

| Fig 19 Boost converter topology                                                          | . 23 |

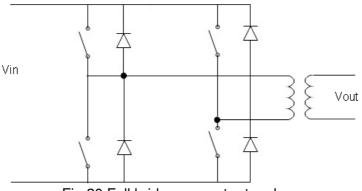

| Fig 20 Full bridge converter topology                                                    | . 23 |

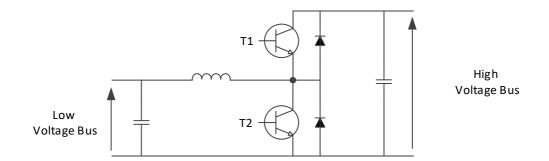

| Fig 21 Basic Bidirectional Converter                                                     | . 24 |

| Fig 22 Bidirectional converter with buck and boost capabilities                          | . 24 |

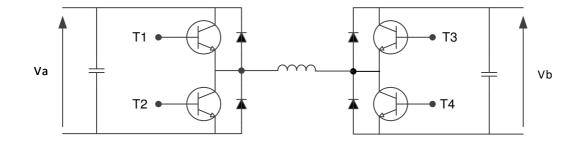

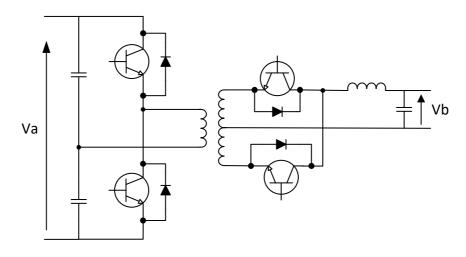

| Fig 23 Full Bridge Isolated Bidirectional Converter                                      | . 25 |

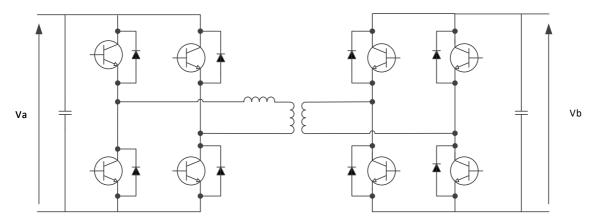

| Fig 24 Half Bridge Bidirectional Converter                                               | . 26 |

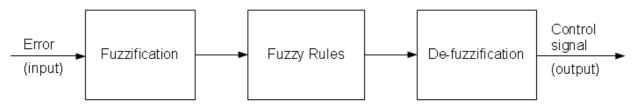

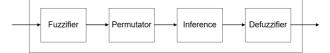

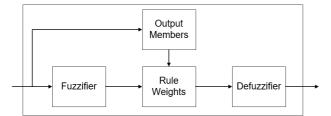

| Fig 25 Fuzzy Logic Controller Topology                                                   |      |

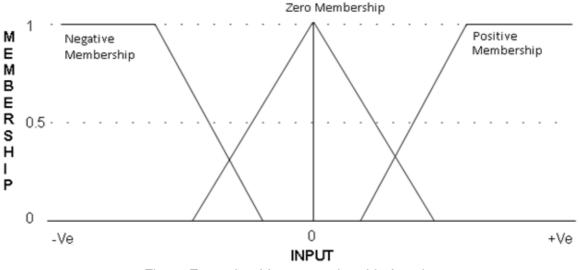

| Fig 26 Example of fuzzy membership functions                                             | . 33 |

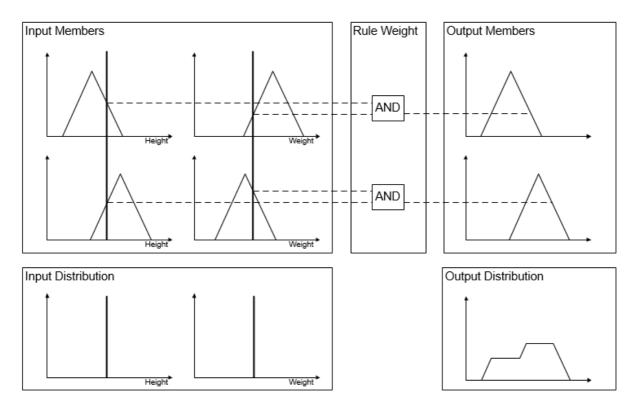

| Fig 27 Operation of a Mamdani Based Inference System                                     |      |

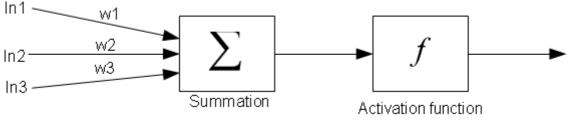

| Fig 28 McCulloch and Pitts Neuron model                                                  |      |

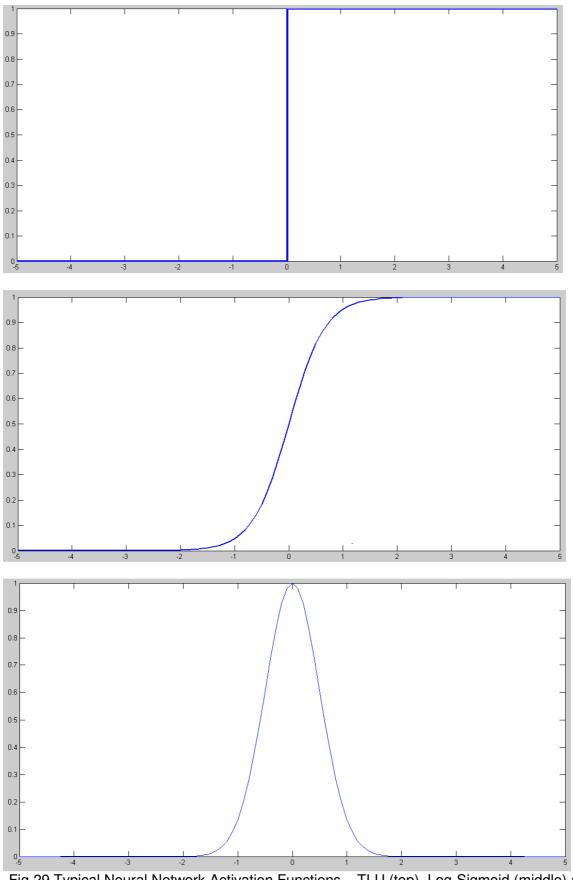

| Fig 29 Typical Neural Network Activation Functions - TLU (top), Log-Sigmoid (middle) and | d    |

| Gaussian (bottom)                                                                        | . 37 |

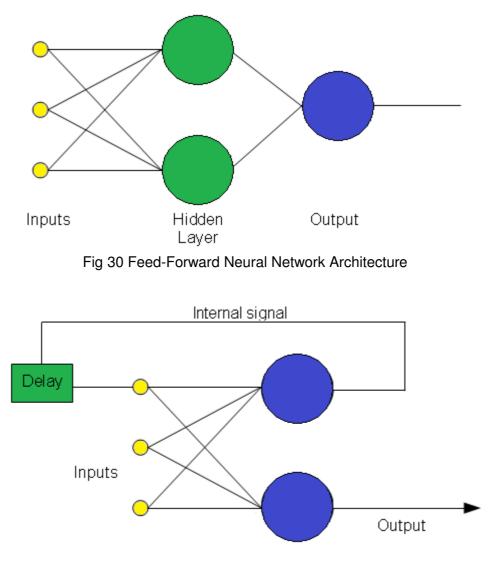

| Fig 30 Feed-Forward Neural Network Architecture                                          |      |

| Fig 31 Recurrent Neural Network Architecture                                             |      |

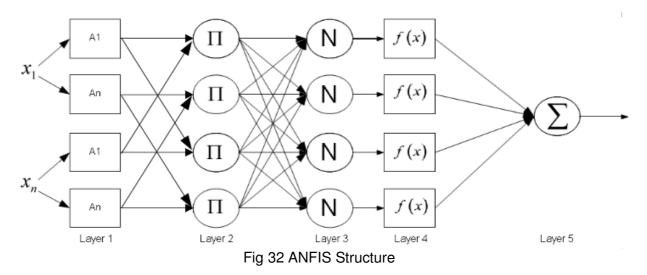

| Fig 32 ANFIS Structure                                                                   |      |

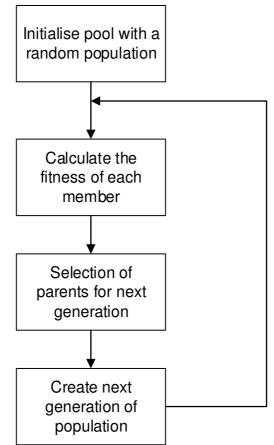

| Fig 33 Flow Diagram of the Genetic Algorithm                                             |      |

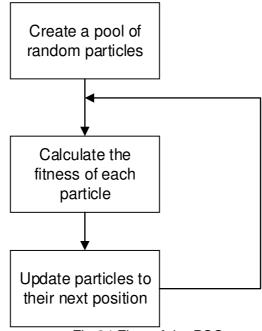

| Fig 34 Flow of the PSO                                                                   |      |

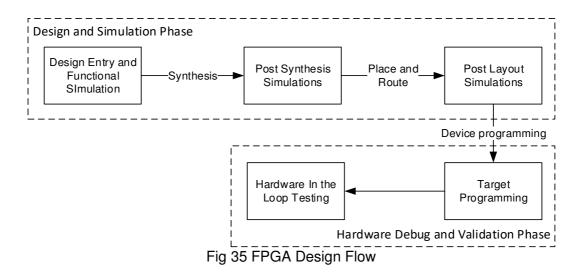

| Fig 35 FPGA Design Flow                                                                  |      |

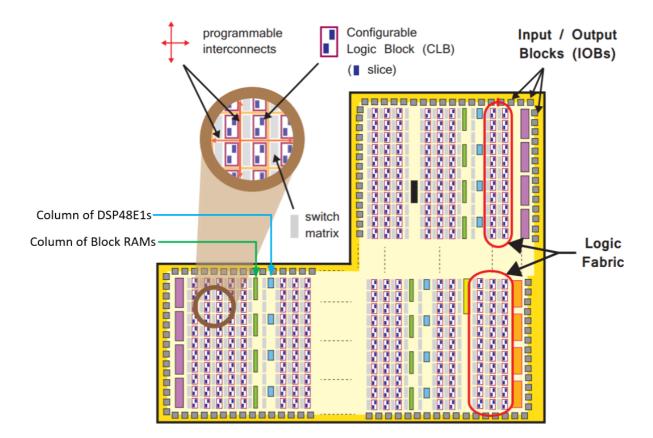

| Fig 36 Example of a Typical FPGA structure (Crockett et al, 2014)                        |      |

| Fig 37 Xilinx Zynq APSOC Architecture (Xilinix(2013))                                    |      |

| Fig 38 PSO PID Tuning Tool Flow                                                          | . 58 |

| Fig 39 Model Tools and Flow Utilised in this Project                                             | . 59 |

|--------------------------------------------------------------------------------------------------|------|

| Fig 40 The Zedboard Hardware Platform                                                            | . 60 |

| Fig 41 System Block Diagram                                                                      | . 62 |

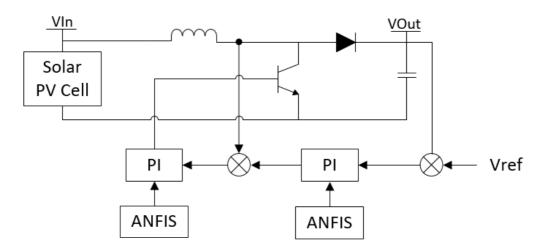

| Fig 42 Control Strategy for the Solar PV Boost Converter Circuit                                 | . 64 |

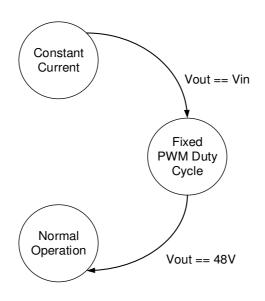

| Fig 43 Soft Start State Machine                                                                  |      |

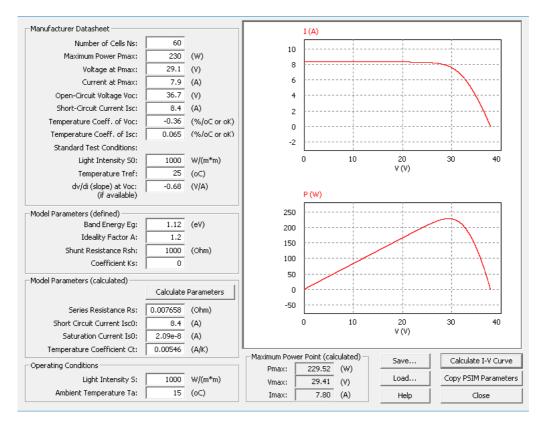

| Fig 44 PSim Model of the BP3230N Solar PV Cell                                                   |      |

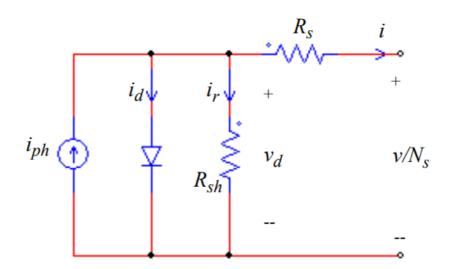

| Fig 45 PSim Solar Cell Equivalent Circuit (Powersim (2017))                                      | . 66 |

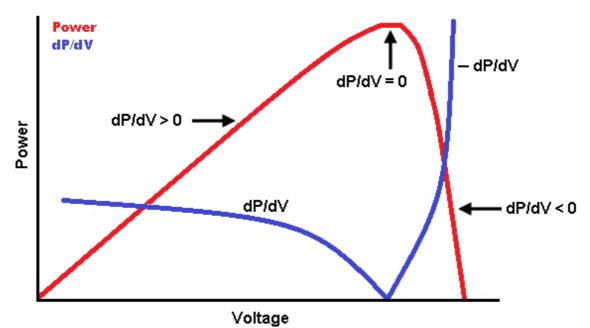

| Fig 46 Example Solar PV Power-Voltage Curve                                                      | . 69 |

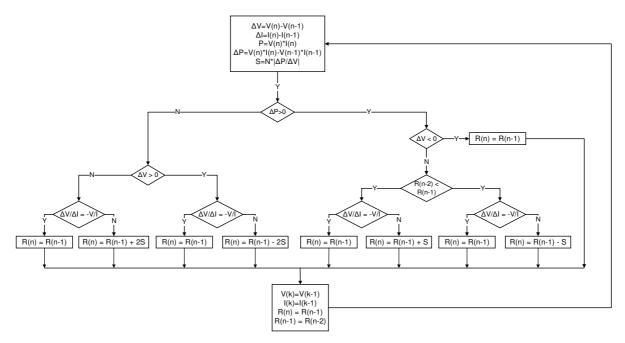

| Fig 47 Load Balancing MPPT Algorithm                                                             | . 70 |

| Fig 48 Particle Swarm Optimization Flow Chart                                                    | . 72 |

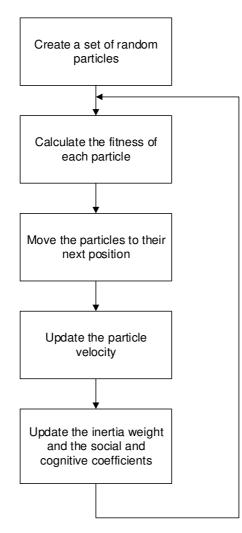

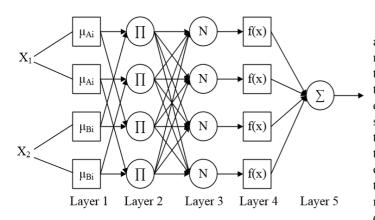

| Fig 49 Example ANFIS Network Architecture                                                        | . 74 |

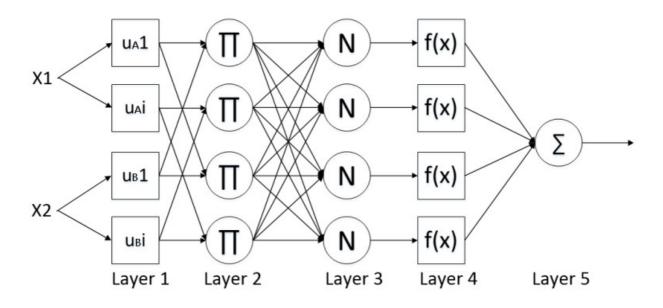

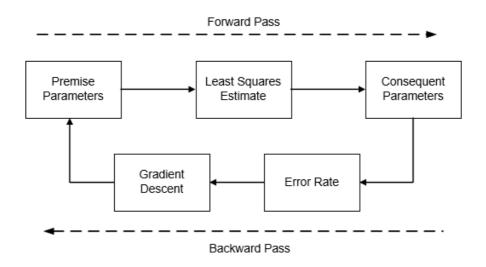

| Fig 50 Flow Chart for the ANFIS Training Algorithm                                               | . 75 |

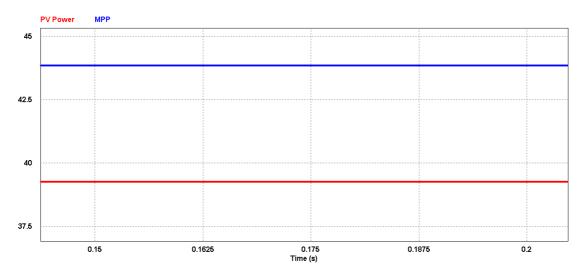

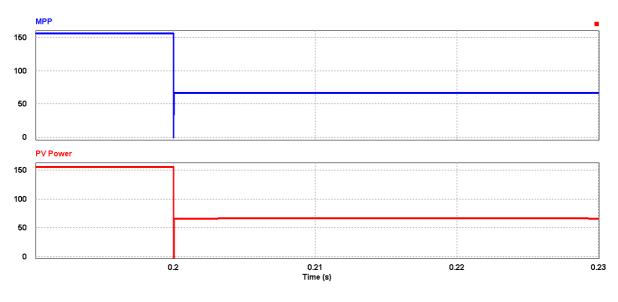

| Fig 51 MPPT Tracking at 200 W/m <sup>2</sup> Steady State Showing the MPP (blue) and the Actual  |      |

| Output Power (red)                                                                               |      |

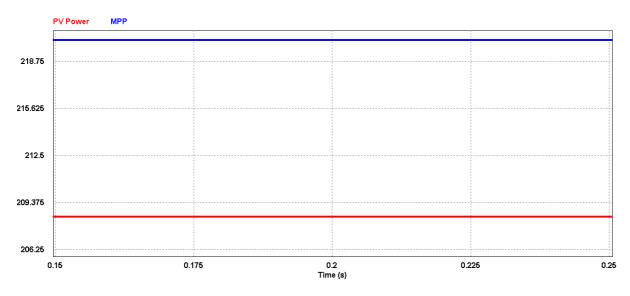

| Fig 52 MPPT Tracking at 1000 W/m <sup>2</sup> Steady State Showing the MPP (blue) and the Actua  | al   |

| Output Power (red)                                                                               | . 78 |

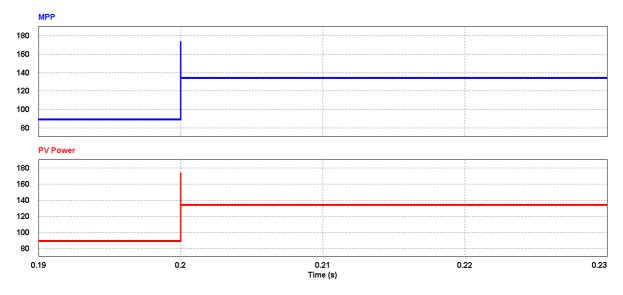

| Fig 53 MPPT Tracking with 200 W/m <sup>2</sup> Step Increase showing the MPP (blue) and the Acti |      |

| Output Power (red)                                                                               |      |

| Fig 54 MPPT Tracking with 400 W/m2 Step Decrease showing the MPP (blue) and the                  |      |

| Actual Output Power (red)                                                                        | . 79 |

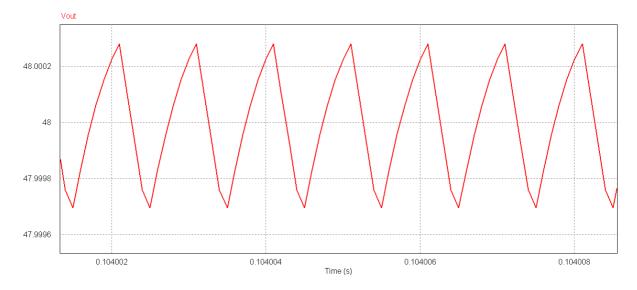

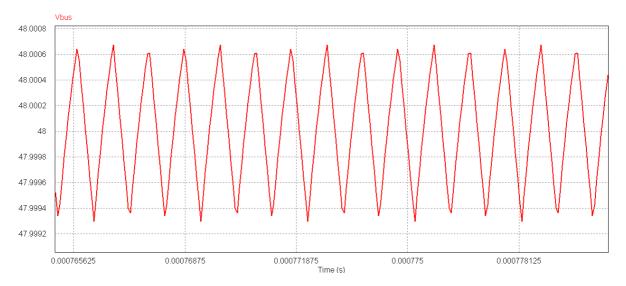

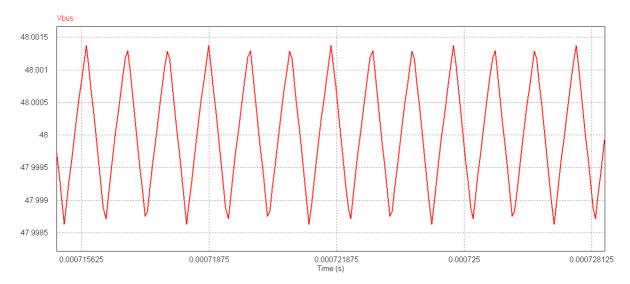

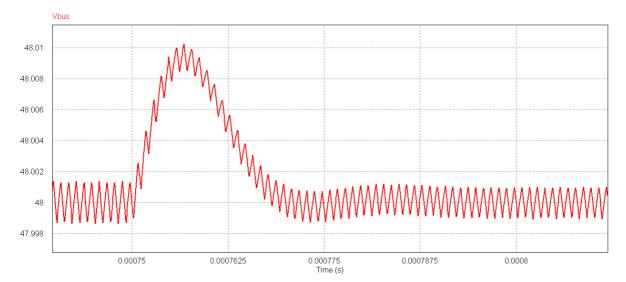

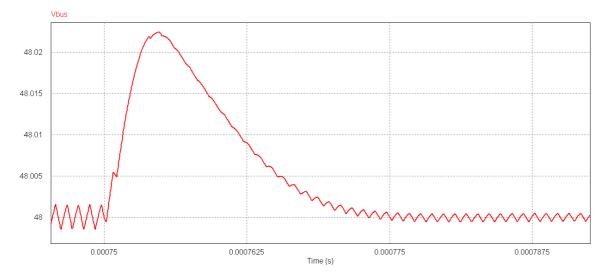

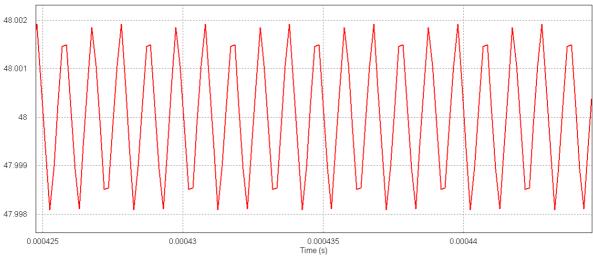

| Fig 55 48VDC Regulator Output Voltage Ripple at 200 W/m <sup>2</sup> irradiance                  |      |

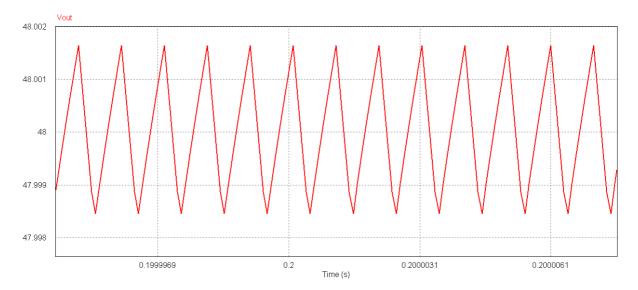

| Fig 56 48VDC Regulator Output Voltage Ripple at 1000 W/m <sup>2</sup>                            |      |

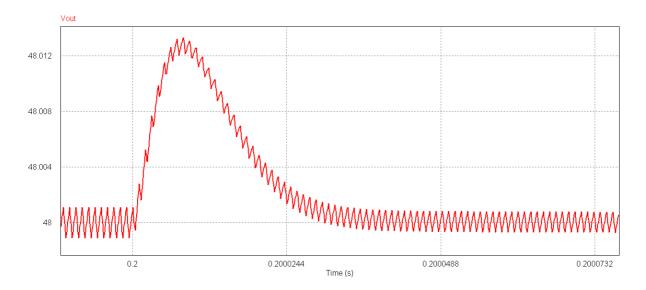

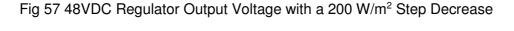

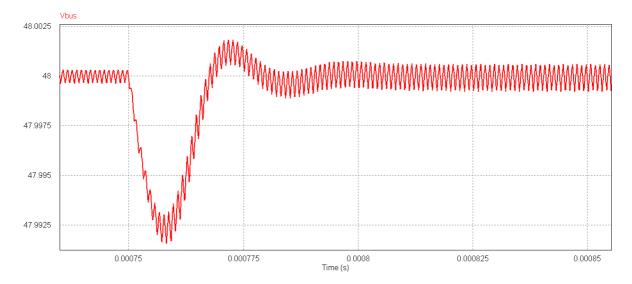

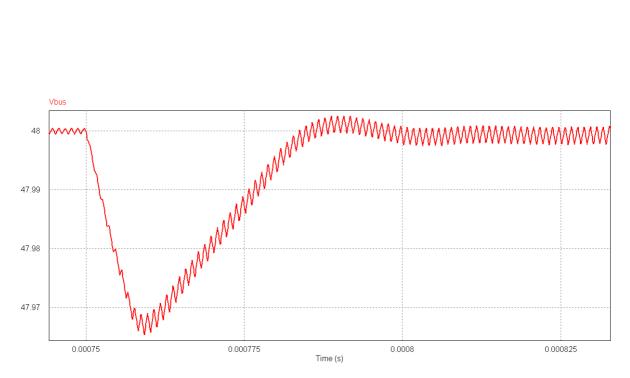

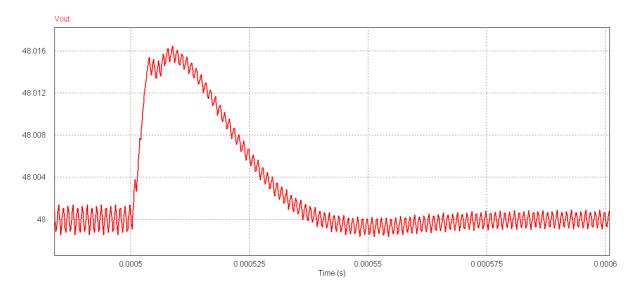

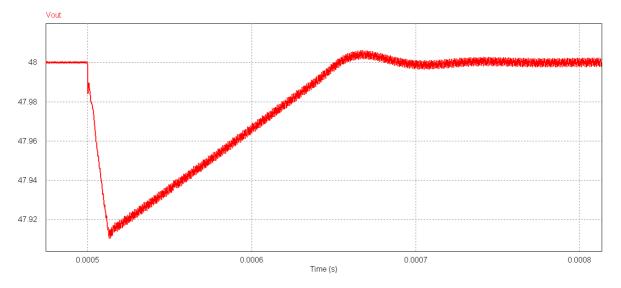

| Fig 57 48VDC Regulator Output Voltage with a 200 W/m <sup>2</sup> Step Decrease                  |      |

| Fig 58 48VDC Regulator Output Voltage with an 800 W/m <sup>2</sup> Step Increase                 |      |

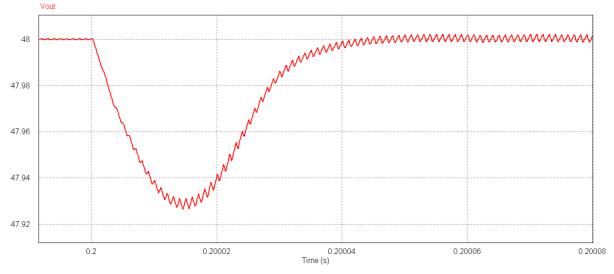

| Fig 59 Simulation of the Boost Converter Soft Start Showing Regulator Output Voltage             |      |

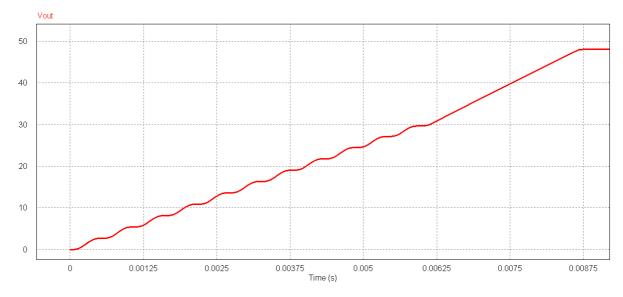

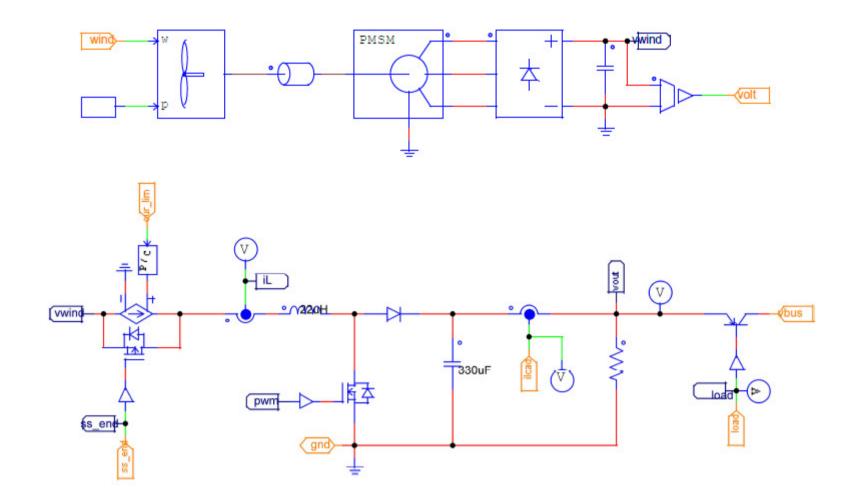

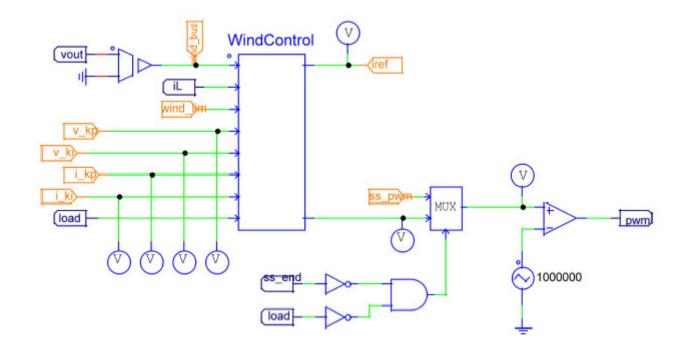

| Fig 60 Wind Turbine Model                                                                        |      |

| Fig 61 Wind Boost Converter Output with 1A Load                                                  |      |

| Fig 62 Wind Boost Output Converter with 2A Load                                                  |      |

| Fig 63 Wind Converter Output with 500mA Step Increase in Load                                    |      |

| Fig 64 Wind Converter Output with 1.5A Step Increase in Load                                     |      |

| Fig 65 Wind Converter Output with 500mA Step Decrease in Load                                    |      |

| Fig 66 Wind Converter Output with 1.5A Step Decrease in Load                                     |      |

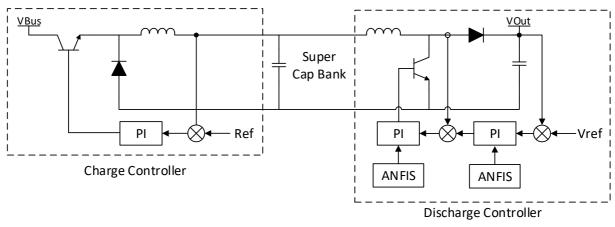

| Fig 67 Super Capacitor Sub System                                                                |      |

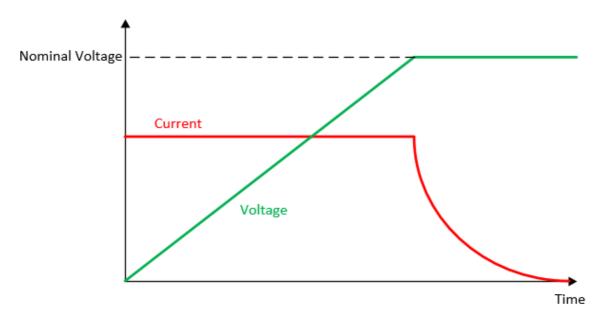

| Fig 68 Super Capacitor Charge Profile                                                            |      |

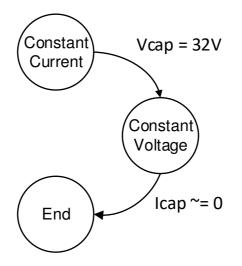

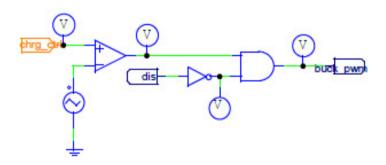

| Fig 69 Super Capacitor Charger States                                                            |      |

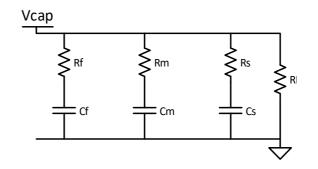

| Fig 70 Three Branch Super Capacitor Model                                                        |      |

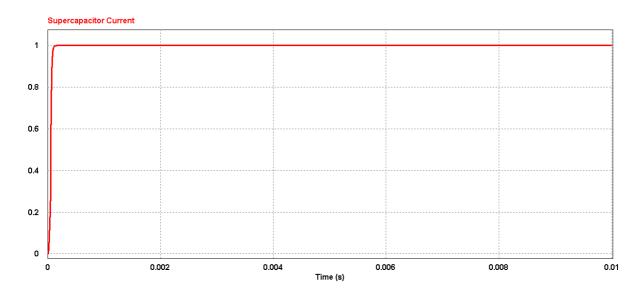

| Fig 71 Supercapacitor Constant Current at 1A                                                     |      |

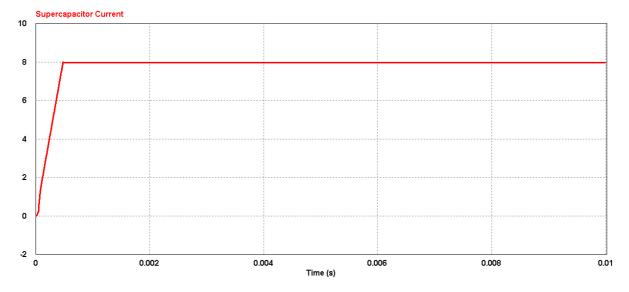

| Fig 72 Supercapacitor Constant Current at 8A                                                     |      |

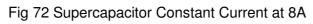

| Fig 73 Supercapacitor Constant Current at 15A                                                    |      |

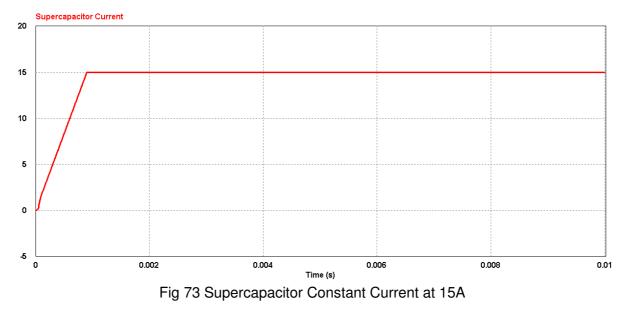

| Fig 74 Supercapacitor Charge Curve at 15A                                                        |      |

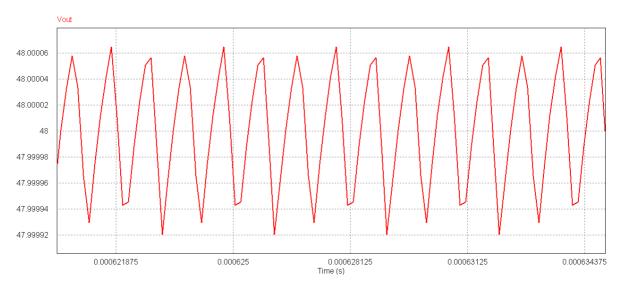

| Fig 75 Super Capacitor Discharge with a Steady 1A Load                                           |      |

|                                                                                                  |      |

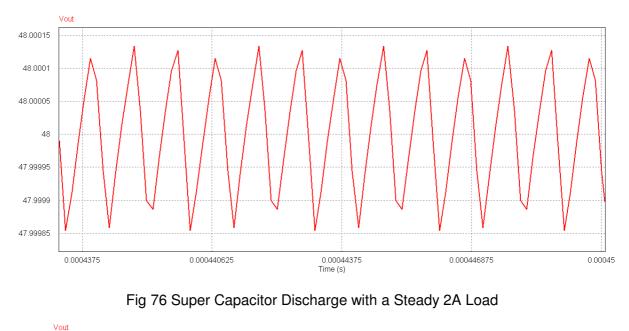

| Fig 76 Super Capacitor Discharge with a Steady 2A Load                                           |      |

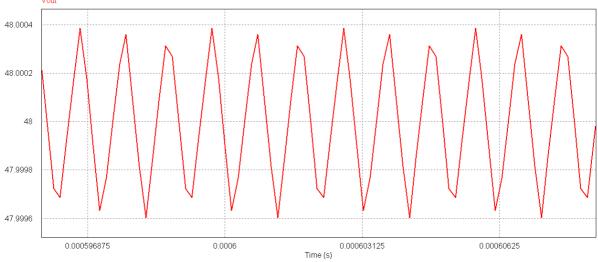

| Fig 77 Super Capacitor Discharge with a Steady 4A Load                                           |      |

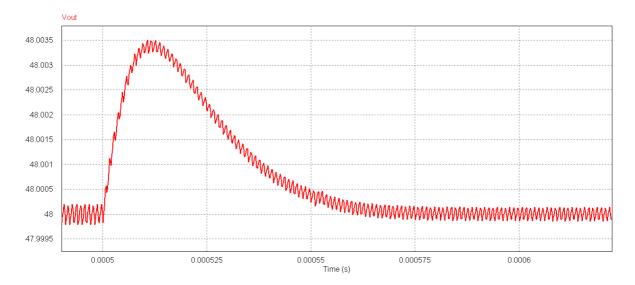

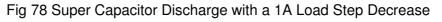

| Fig 78 Super Capacitor Discharge with a 1A Load Step Decrease                                    |      |

| Fig 79 Super Capacitor Discharge with a 4A Load Step Increase                                    |      |

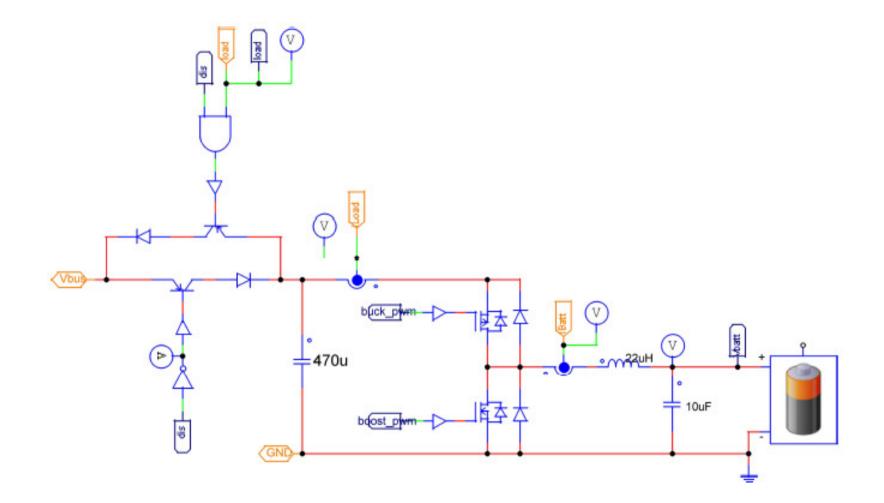

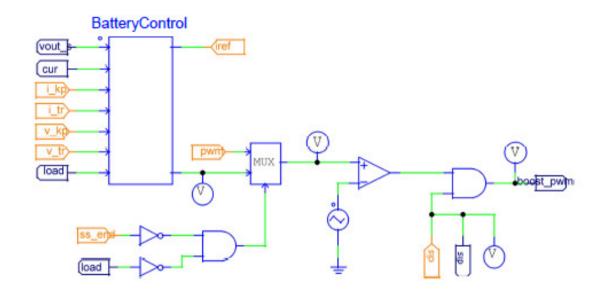

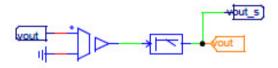

| Fig 80 Battery Subsystem Circuit                                                                 |      |

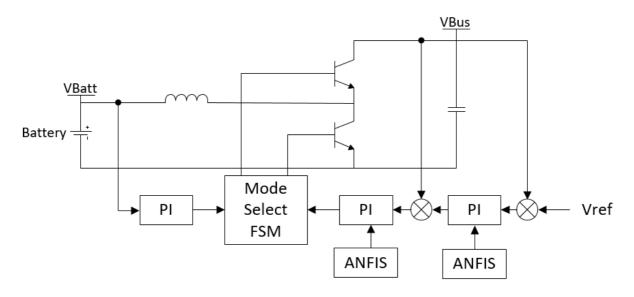

| Fig 81 Battery Charging Profile                                                                  |      |

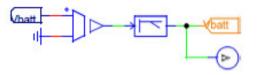

| Fig 82 Battery Charger State Machine                                                             | .97  |

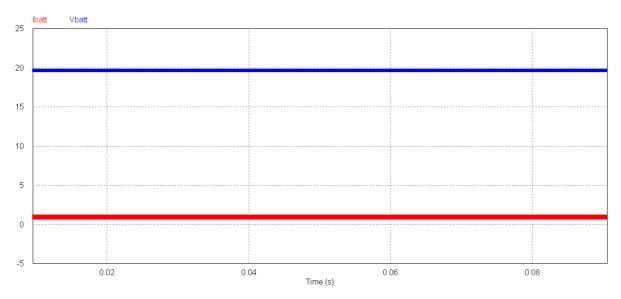

| Fig 83 Battery Charge Constant Current at 1A                                                    | 99  |

|-------------------------------------------------------------------------------------------------|-----|

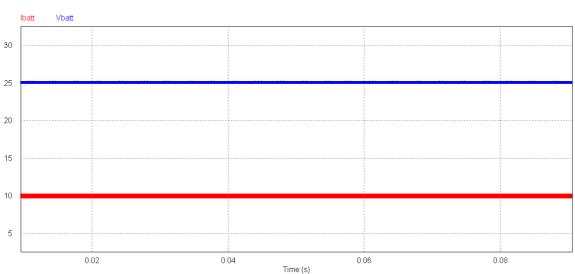

| Fig 84 Battery Charge Constant Current at 10A                                                   |     |

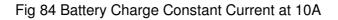

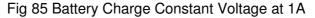

| Fig 85 Battery Charge Constant Voltage at 1A                                                    |     |

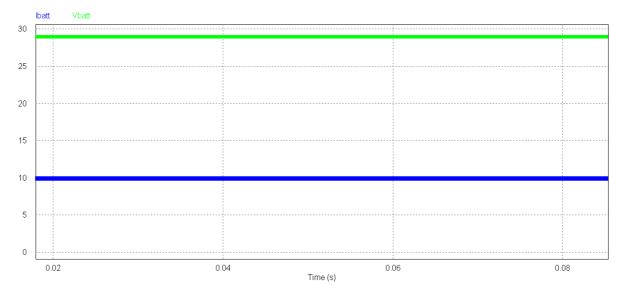

| Fig 86 Battery Charge Constant Voltage at 10A                                                   |     |

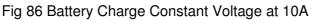

| Fig 87 Battery Discharge Controller with a 1A Load                                              |     |

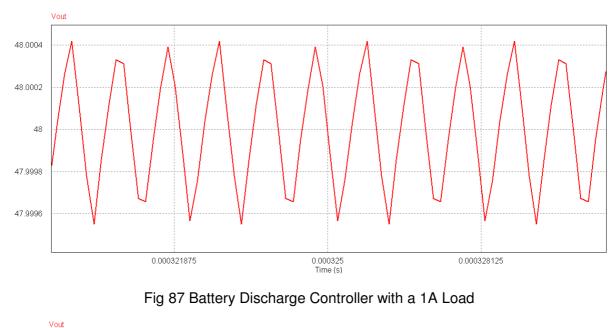

| Fig 88 Battery Discharge Controller with a 4A Load                                              |     |

| Fig 89 Battery Discharge with a 1A Load Step Decrease                                           |     |

| Fig 90 Battery Discharge with a 4A Load Step Increase                                           | 102 |

| Fig 91 System Block Diagram                                                                     |     |

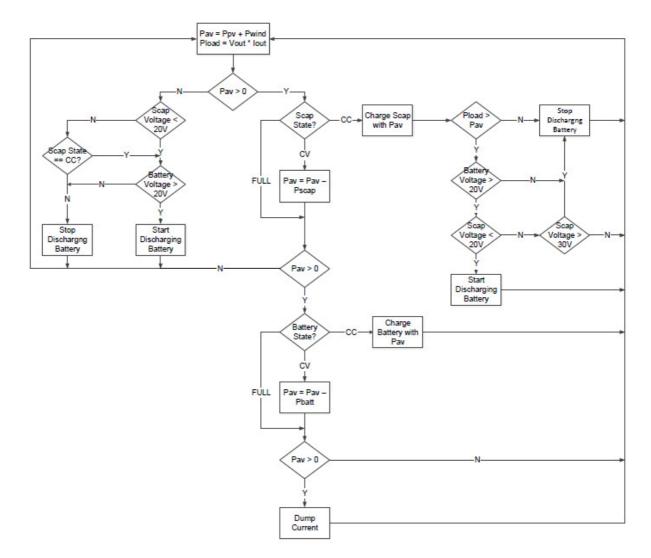

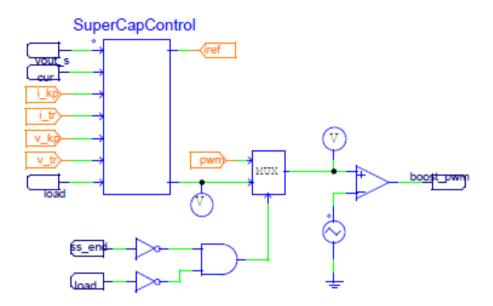

| Fig 92 Power Control Algorithm Flow Chart                                                       |     |

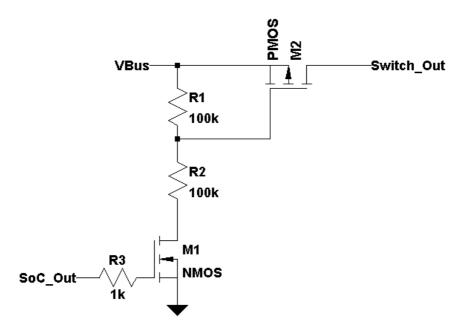

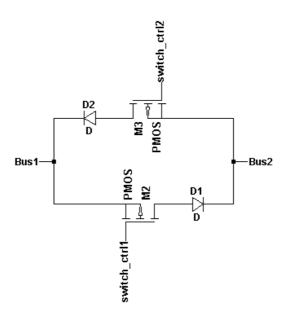

| Fig 93 High Side PMOS Based Switch Circuit                                                      |     |

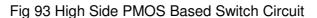

| Fig 94 Simulation Results of the High Side PMOS Based Switch Circuit                            |     |

| Fig 95 Bidirectional PMOS Based Circuit                                                         |     |

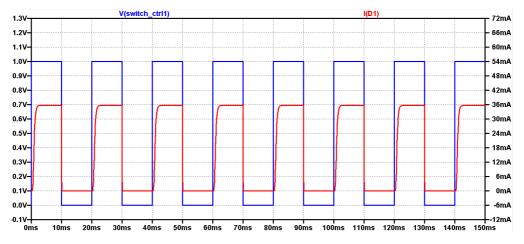

| Fig 96 Bidirectional Switch Simulation with Current Flowing From Bus1 to Bus2                   |     |

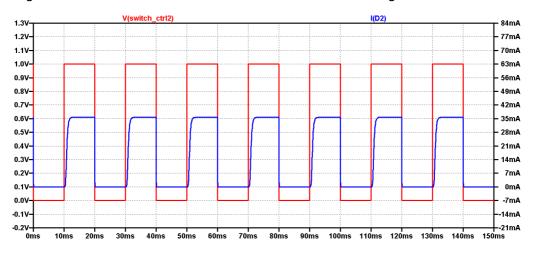

| Fig 97 Bidirectional Switch Simulation with Current Flowing From Bus2 to Bus1                   |     |

| Fig 98 Example of the Buck Converter Soft Start Function                                        |     |

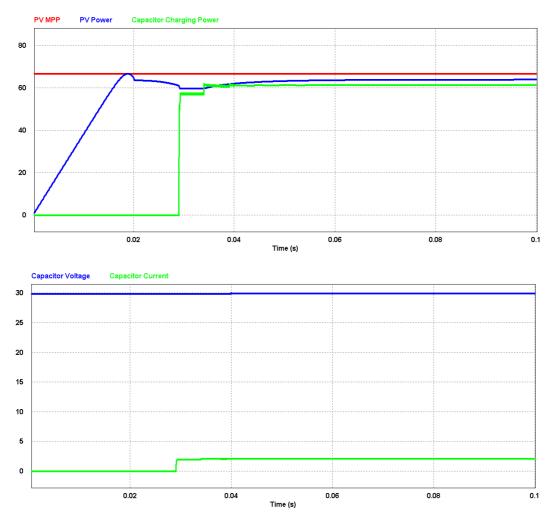

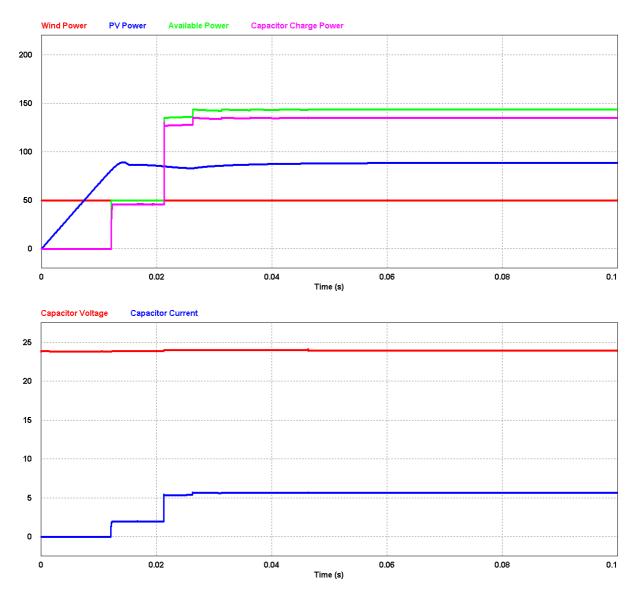

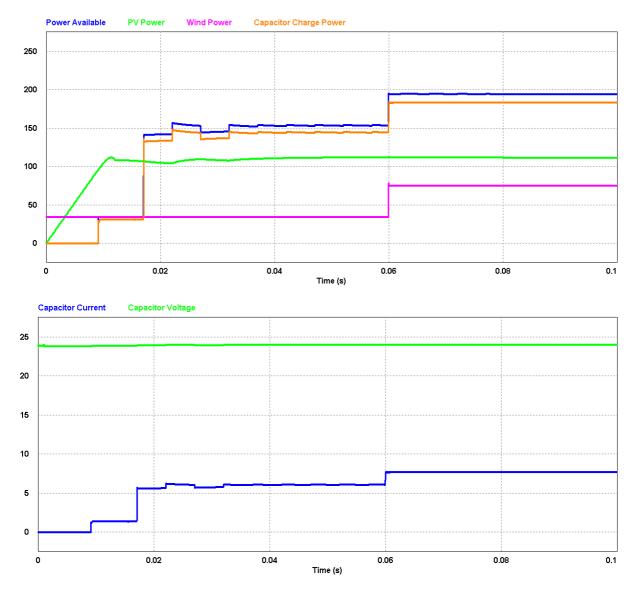

| Fig 99 Solar PV Cell Power and Supercapacitor Charging Power with 300 w/m² Irradianc            |     |

|                                                                                                 |     |

| Fig 100 Solar PV Cell Power and Supercapacitor Charging Power with 800 w/m2 Irradian            |     |

|                                                                                                 |     |

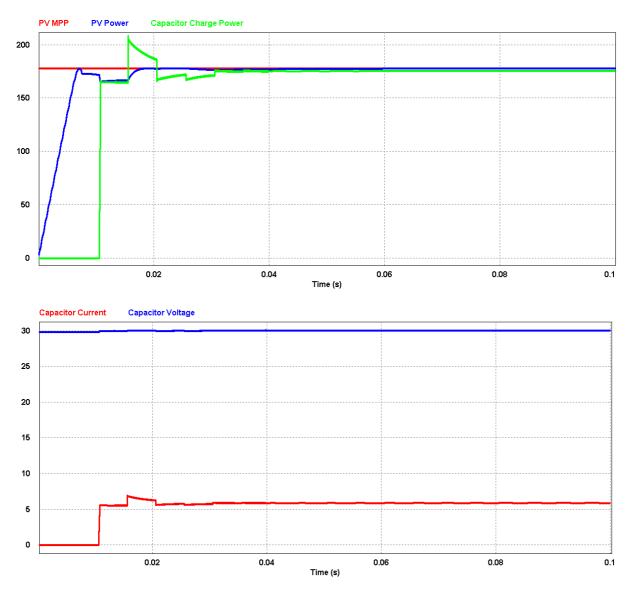

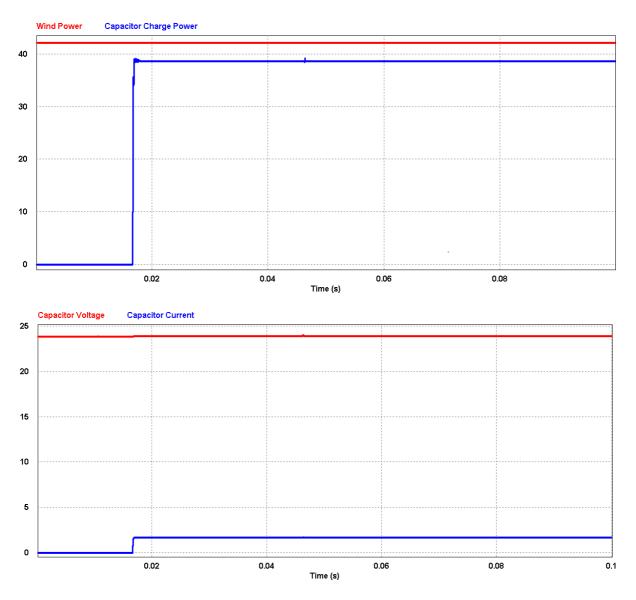

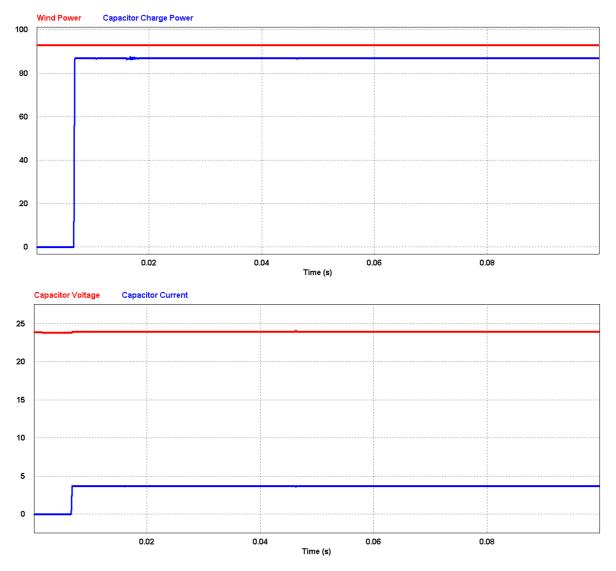

| Fig 101 Wind Turbine Power and Supercapacitor Charging Power with 6 m/s Wind Speed              |     |

|                                                                                                 |     |

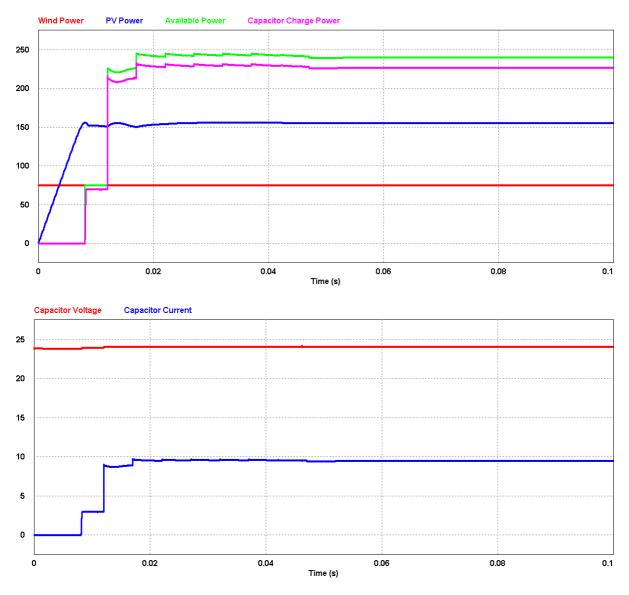

| Fig 102 Wind Turbine Power and Supercapacitor Charging Power with 12 m/s Wind Spee              |     |

|                                                                                                 |     |

| Fig 103 Wind Turbine, Solar PV Cell and Supercapacitor Charging Power with 6 m/s Win            |     |

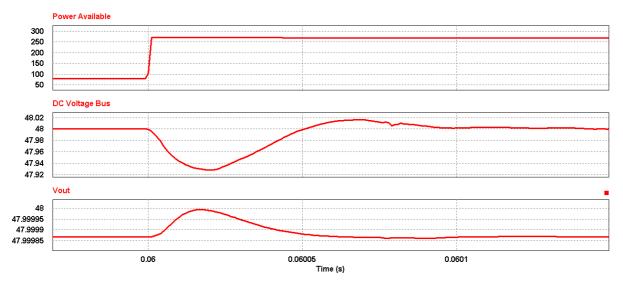

| Speed and 400 w/m <sup>2</sup> Irradiance                                                       |     |

| Fig 104 Wind Turbine, Solar PV Cell and Supercapacitor Charging Power with 10 m/s Wi            |     |

| Speed and 800 w/m <sup>2</sup> Irradiance.                                                      |     |

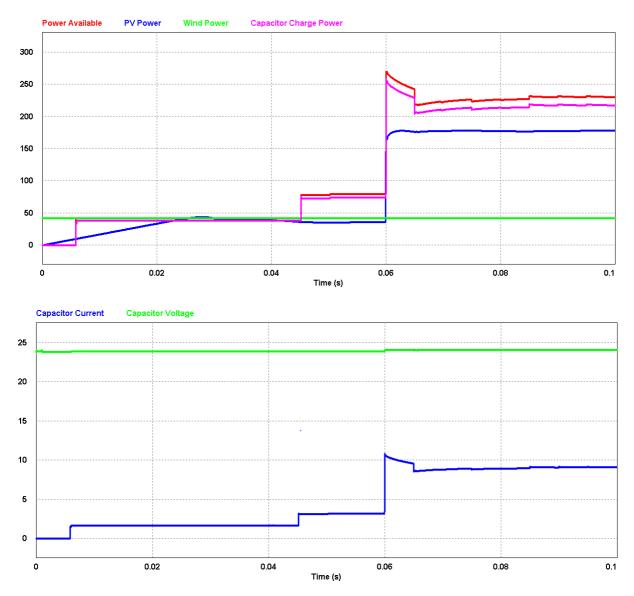

| Fig 105 Wind Turbine, Solar PV Cell and Supercapacitor Charging Power with 6 m/s Win            |     |

| Speed and a 600 w/m <sup>2</sup> Step Increase in Irradiance                                    |     |

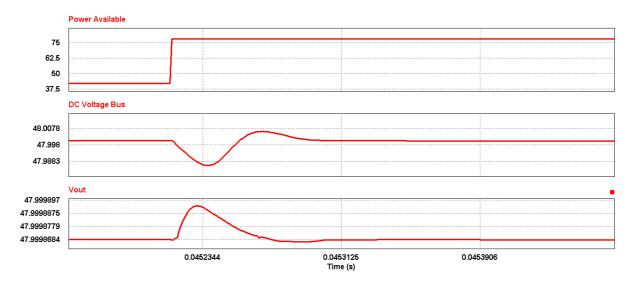

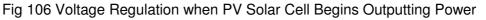

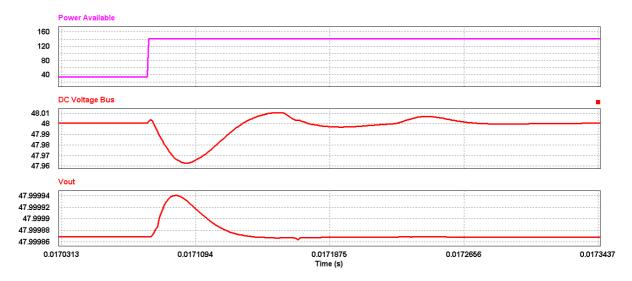

| Fig 106 Voltage Regulation when PV Solar Cell Begins Outputting Power                           |     |

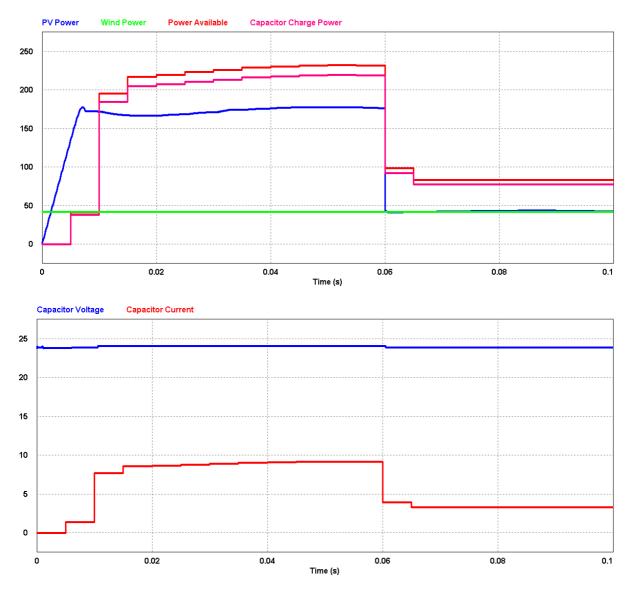

| Fig 107 Voltage Regulation when Step Decrease Occurs in PV Solar Cell Power Product             |     |

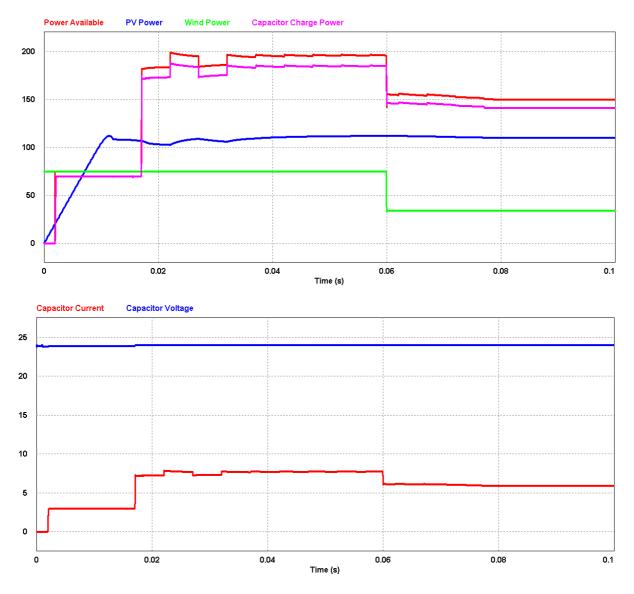

| Fig. 100 Mind Turking Color DV Coll and Current protection Observing Device with Curres Win     |     |

| Fig 108 Wind Turbine, Solar PV Cell and Supercapacitor Charging Power with 6 m/s Win            |     |

| Speed and a 600 w/m <sup>2</sup> Step Decrease in Irradiance                                    |     |

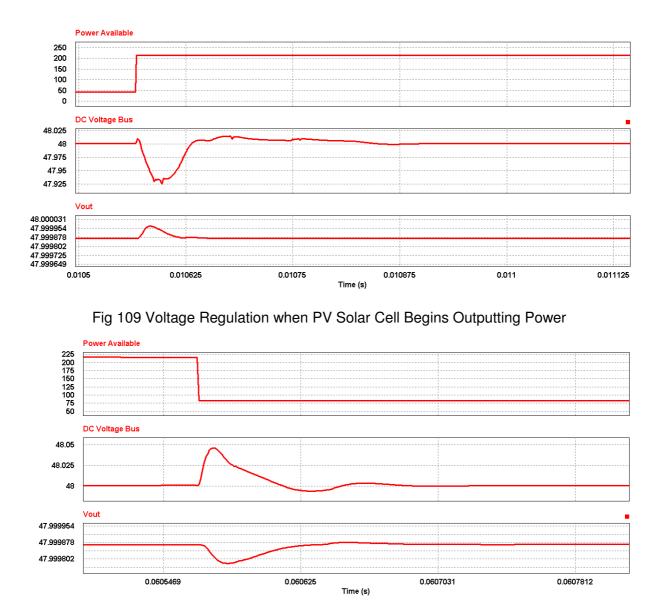

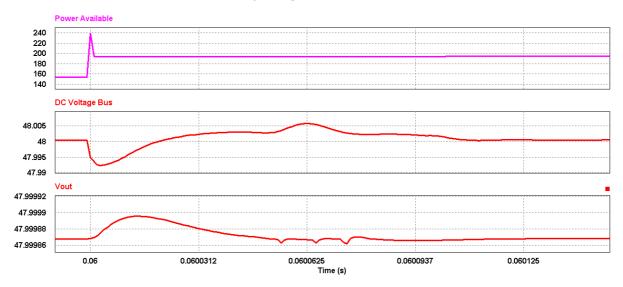

| Fig 109 Voltage Regulation when PV Solar Cell Begins Outputting Power                           |     |

| Fig 110 Voltage Regulation when Step Decrease Occurs in PV Solar Cell Power Product             |     |

| Fig 111 Wind Turbine, Solar PV Cell and Supercapacitor Charging Power with 500 w/m <sup>2</sup> | 120 |

| Irradiance and 5 m/s Step Increase in Wind Speed                                                | 101 |

|                                                                                                 | 121 |

| Fig 112 Voltage Regulation During Wind Step Increase Test when PV Solar Cell Begins             | 100 |

| Outputting Power<br>Fig 113 Voltage Regulation when Step Increase in Wind Speed                 |     |

| Fig 114 Wind Turbine, Solar PV Cell and Supercapacitor Charging Power with 500 w/m <sup>2</sup> | 122 |

| Irradiance and 5 m/s Step Decrease in Wind Speed                                                | 100 |

| Fig 115 Voltage Regulation During Wind Step Decrease Test when PV Solar Cell Begins             |     |

| Outputting Power                                                                                |     |

| Fig 116 Voltage Regulation when Step Decrease in Wind Speed                                     |     |

| The the voltage regulation when ever beerease in while opeed                                    | 164 |

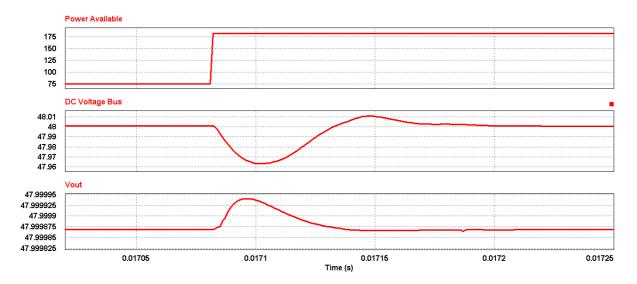

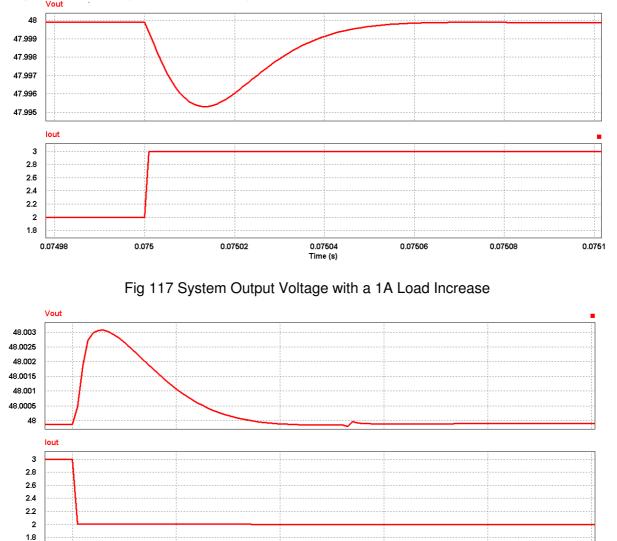

| Fig 117 System Output Voltage with a 1A Load Increase                                                                           |       |

|---------------------------------------------------------------------------------------------------------------------------------|-------|

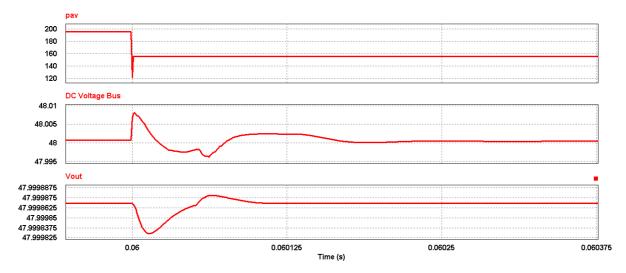

| Fig 118 System Output Voltage with a 1A Load Decrease                                                                           |       |

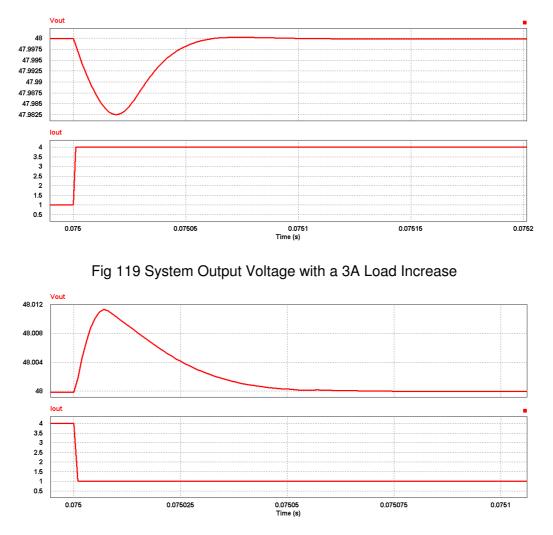

| Fig 119 System Output Voltage with a 3A Load Increase                                                                           | 126   |

| Fig 120 System Output Voltage with a 3A Load Decrease                                                                           |       |

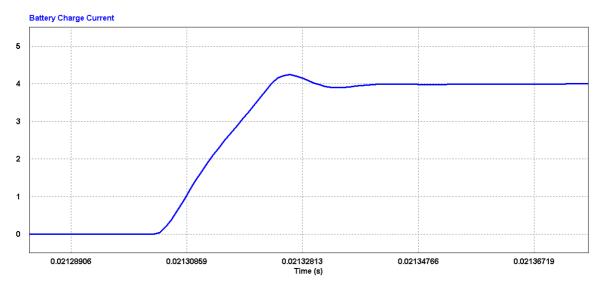

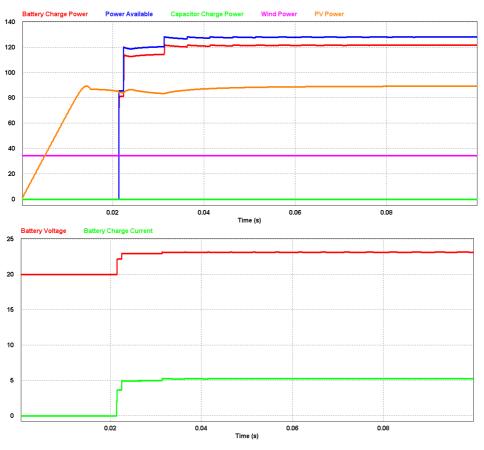

| Fig 121 Battery Charging Simulation with a Small Charge Current                                                                 |       |

| Fig 122 System Battery Charging Simulation with a Large Charge Current                                                          |       |

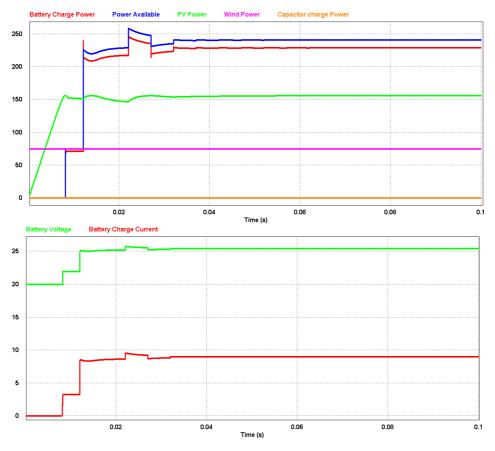

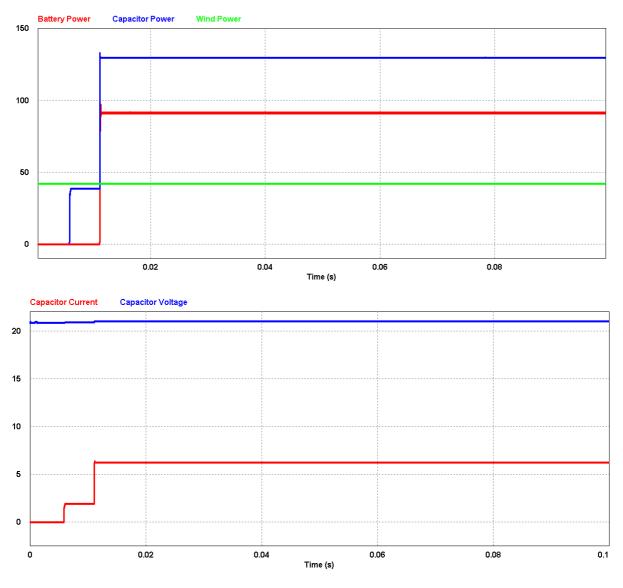

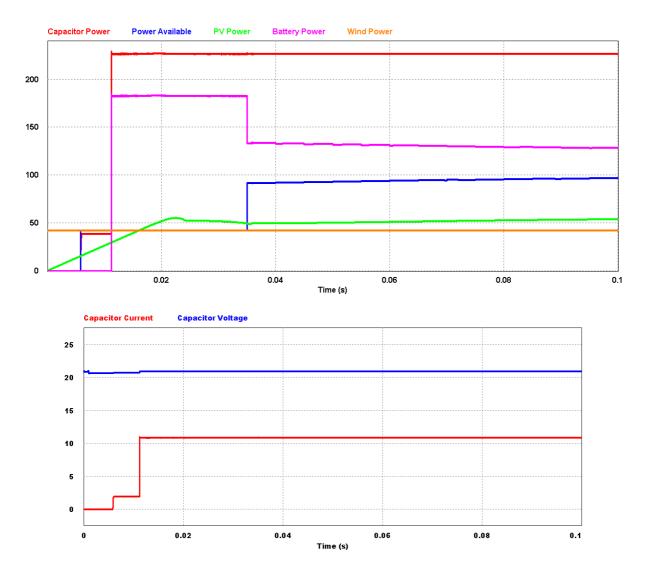

| Fig 123 Supercapacitor Being Charged at a Rate of 50W by the Battery                                                            | 129   |

| Fig 124 Supercapacitor Being Charged at a Rate of 200W by the Battery                                                           | 130   |

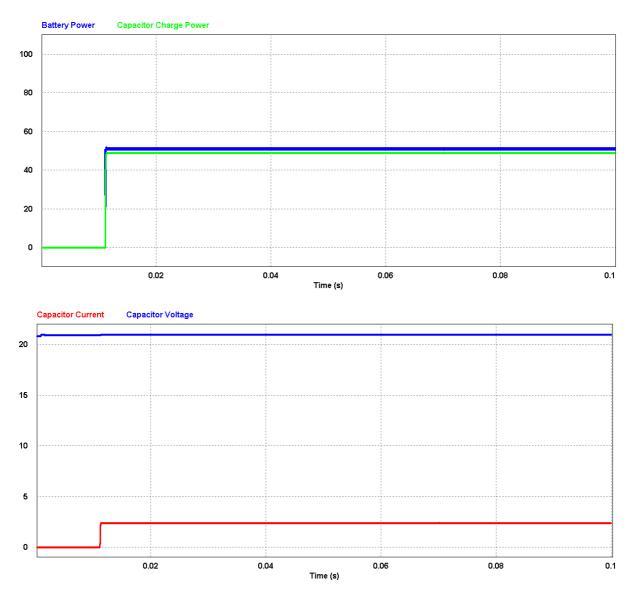

| Fig 125 Supercapacitor Being Charged at a Rate of 130W by the Battery and Wind Turbi                                            |       |

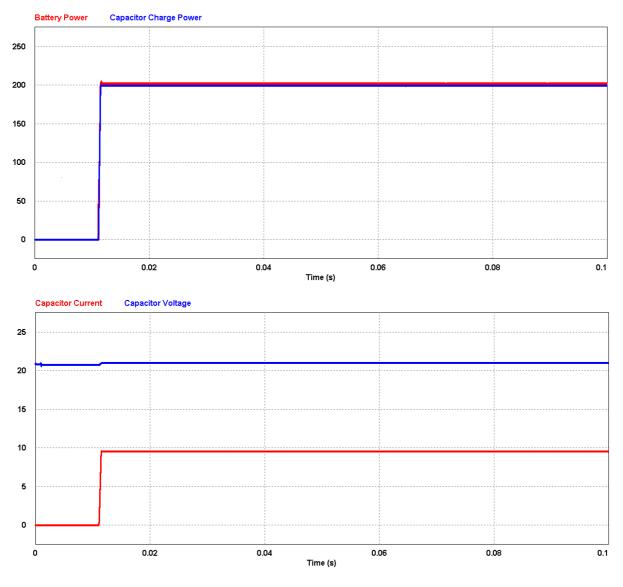

|                                                                                                                                 |       |

| Fig 126 Supercapacitor Being Charged at a Rate of 221W by the Battery, Solar PV Cell a                                          |       |

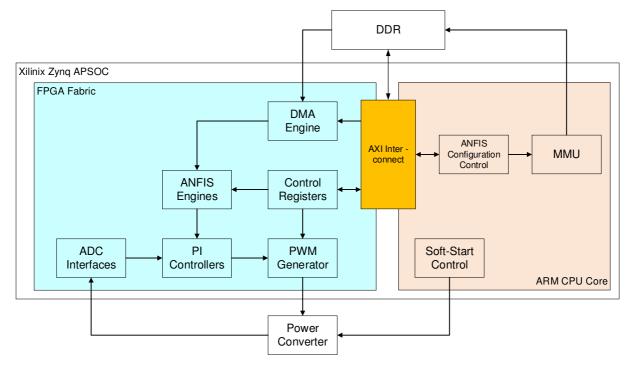

| Wind Turbine<br>Fig 127 Block Diagram of the APSOC Architecture                                                                 |       |

|                                                                                                                                 | 134   |

| Fig 128 Block Diagram of the Power Converter Controller as Implemented in the FPGA                                              | 100   |

| Fabric                                                                                                                          |       |

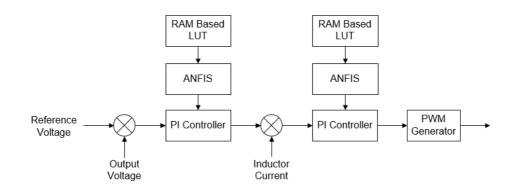

| Fig 129 Block Diagram of the Sequential ANFIS Architecture for use in FPGAs                                                     |       |

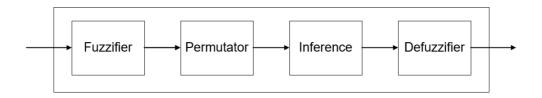

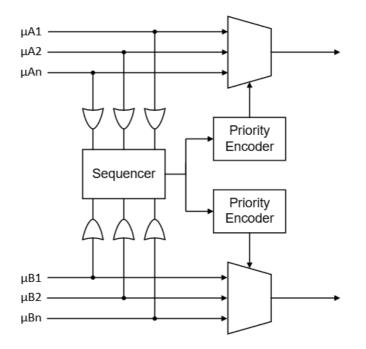

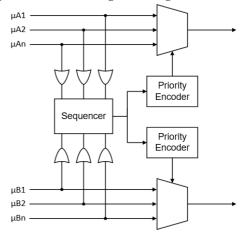

| Fig 130 Block Diagram of the Novel Permutator                                                                                   |       |

| Fig 131 VHDL Function to determine when a Signal is a Non-Zero Value                                                            | 138   |

| Fig 132 VHDL Code Showing How a Member Map is Created That Indicates Which                                                      | 100   |

| Members are Non-Zero Values                                                                                                     |       |

| Fig 133 VHDL Code Showing the Implementation of the Novel Permutator Multiplexers a                                             |       |

| Priority Encoders.                                                                                                              |       |

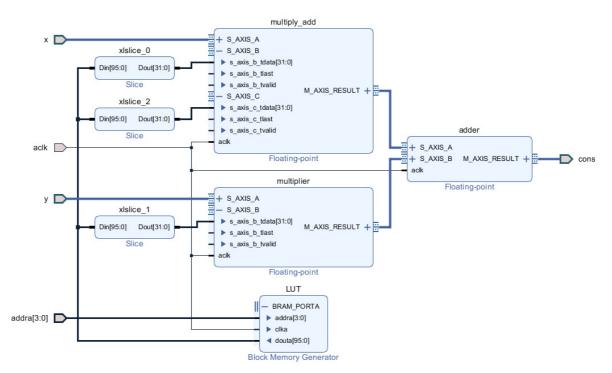

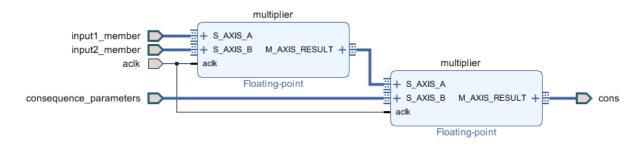

| Fig 134 Consequence Parameter Circuit Diagram Taken from Xilinx Vivado Software                                                 |       |

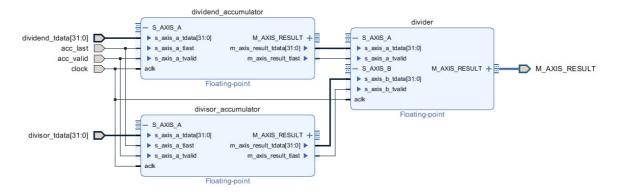

| Fig 135 Inference Engine Circuit Diagram Taken from Xilinx Vivado Software                                                      |       |

| Fig 136 Defuzzifier Circuit Block Diagram as Taken from Xilinix Vivado Software                                                 |       |

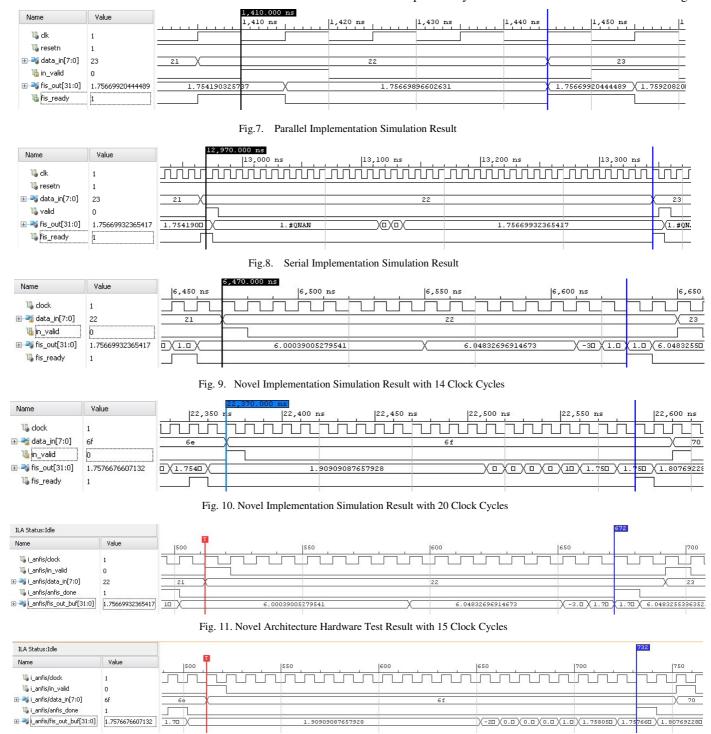

| Fig 137 Existing ANFIS Calculation Showing 41 Clock Cycles Between the Start and Enc                                            |       |

| Calculation Pulses                                                                                                              |       |

| Fig 138 Existing Permutator with Sixteen Clock Cycles, as shown by the Assertion Time                                           |       |

| the Out Valid Signal                                                                                                            | 142   |

| Fig 139 Novel ANFIS Calculation Showing 27 Clock Cycles Between the Start and End                                               | 1 4 0 |

| Calculation Pulses                                                                                                              | 142   |

| Fig 140 Novel ANFIS Calculation Showing 37 Clock Cycles Between the Start and End                                               | 140   |

| Calculation Pulses<br>Fig 141 Novel Permutator with Two Clock Cycles, as shown by the Assertion Time of the                     |       |

|                                                                                                                                 |       |

| Out Valid Signal                                                                                                                |       |

| Fig 142 Novel Permutator with Fourteen Clock Cycles, as shown by the Assertion Time of the Out Valid Signal                     |       |

| the Out Valid Signal                                                                                                            | 143   |

| Fig 143 Novel ANFIS Calculation Showing 27 Clock Cycles Between the Start and End                                               | 140   |

| Calculation Pulses During Hardware Testing<br>Fig 144 Novel ANFIS Calculation Showing 37 Clock Cycles Between the Start and End | 143   |

|                                                                                                                                 | 140   |

| Calculation Pulses During Hardware Testing<br>Fig 145 Summary of the STA for the Existing ANFIS Implementation                  |       |

| Fig 146 Summary of the STA for the Novel ANFIS Implementation                                                                   |       |

|                                                                                                                                 |       |

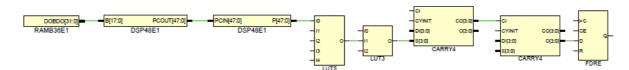

| Fig 147 Circuit Diagram of the Worst Timing Path in the ANFIS FPGA Implementations<br>Fig 148 PWM Generator Block Diagram       |       |

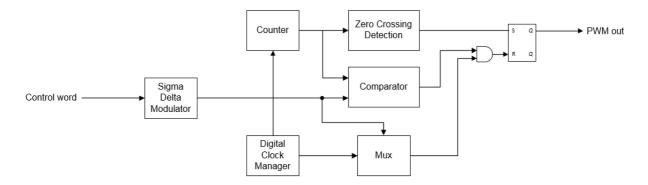

| Fig 148 FWM Generator Block Diagram                                                                                             |       |

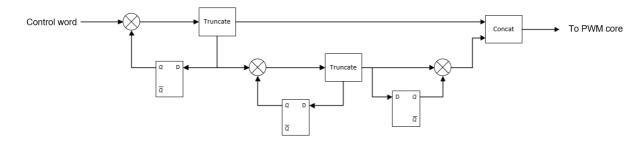

| Fig 150 VHDL Code Implementing the Sigma Delta Modulator Circuit                                                                |       |

|                                                                                                                                 |       |

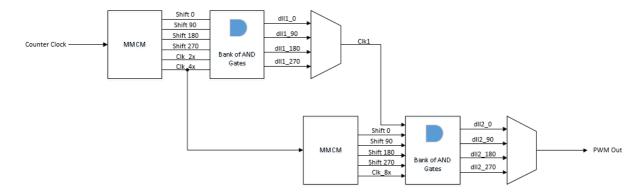

| Fig 151 Digital Clock Manager Block Diagram                                                                                     | 14/   |

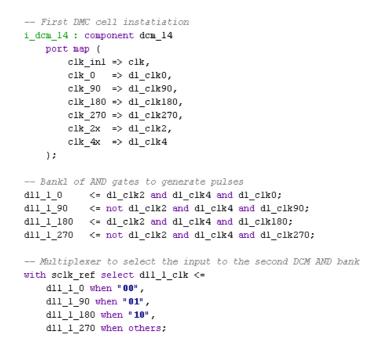

| Fig 152 RTL Code Showing Instantiation of the DCM, Bank of AND Gates and Multiplexo     | r   |

|-----------------------------------------------------------------------------------------|-----|

| Required to Generate the Reset Pulse                                                    |     |

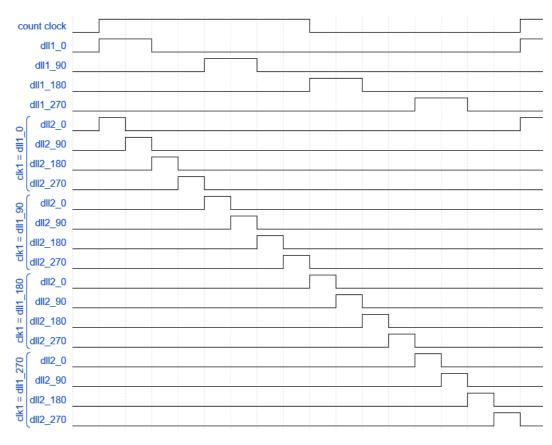

| Fig 153 Digital Clock Manager Waveforms                                                 | 148 |

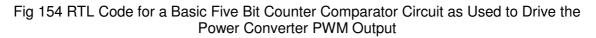

| Fig 154 RTL Code for a Basic Five Bit Counter Comparator Circuit as Used to Drive the   |     |

| Power Converter PWM Output                                                              |     |

| Fig 155 PWM Simulation with 80% Duty Cycle                                              | 149 |

| Fig 156 Hardware Test with 80% Duty Cycle                                               | 150 |

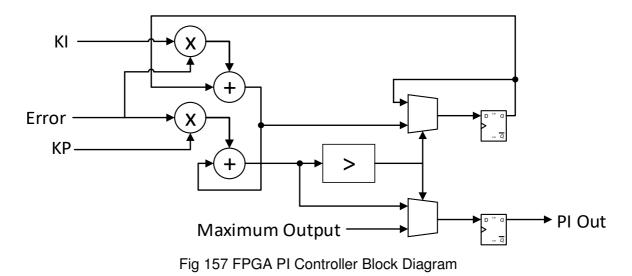

| Fig 157 FPGA PI Controller Block Diagram                                                |     |

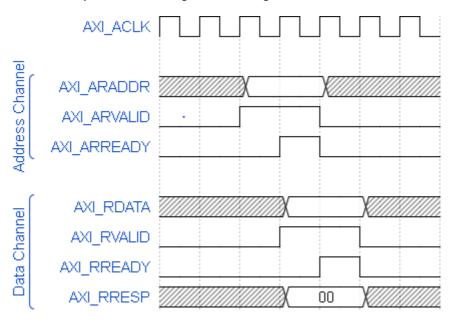

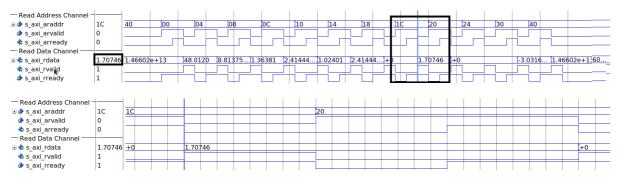

| Fig 158 AXI-Lite Bus Behaviour During a Read                                            | 152 |

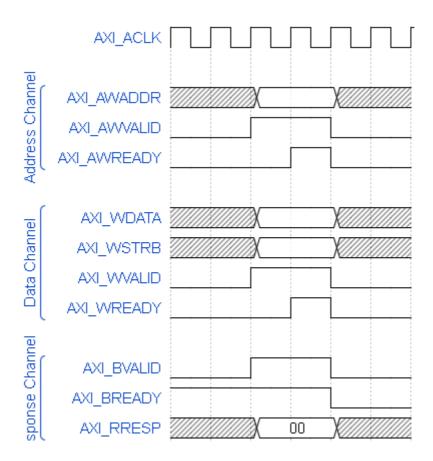

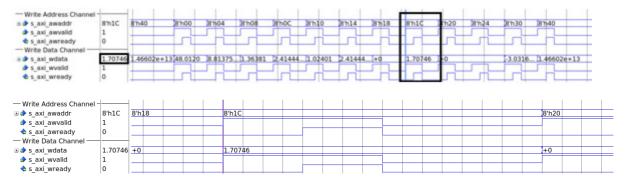

| Fig 159 AXI-Lite Bus Behaviour During a Write                                           | 153 |

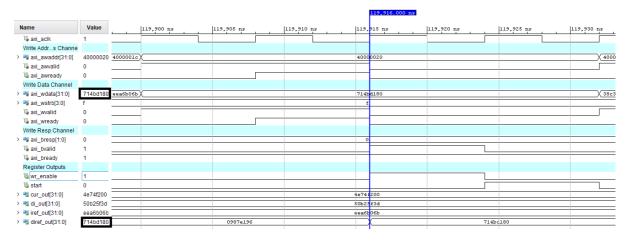

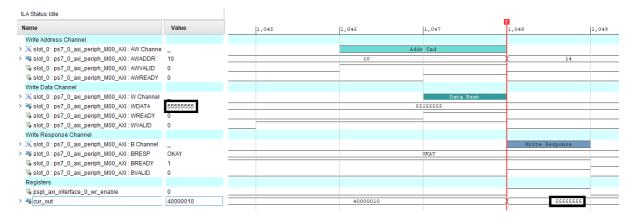

| Fig 160 AXI Register Write Simulation                                                   | 153 |

| Fig 161 AXI Register Read Simulation                                                    | 154 |

| Fig 162 AXI Register Write HW Test                                                      | 154 |

| Fig 163 AXI Register Read HW Test                                                       | 154 |

| Fig 164 Scatter-Gather DMA System                                                       | 155 |

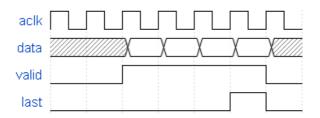

| Fig 165 AXI-Stream Bus Behaviour                                                        | 156 |

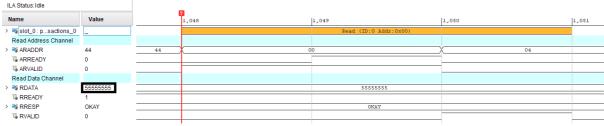

| Fig 166 DMA Data Transfer Simulation                                                    | 156 |

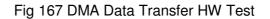

| Fig 167 DMA Data Transfer HW Test                                                       | 156 |

| Fig 168 Logic Utilisation for the Novel Power Converter Controller FPGA Core            | 157 |

| Fig 169 Summary of the STA for the FPGA Design                                          |     |

| Fig 170 Test Setup for the Novel Power Converter Control Solution                       | 159 |

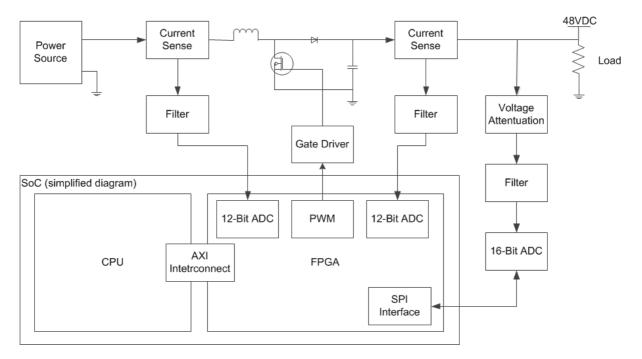

| Fig 171 High Side Current Sense Circuit using the AD8212 IC                             |     |

| Fig 172 Simulation of the Load Current Sense Circuit Showing Current (blue) and Sensor  | -   |

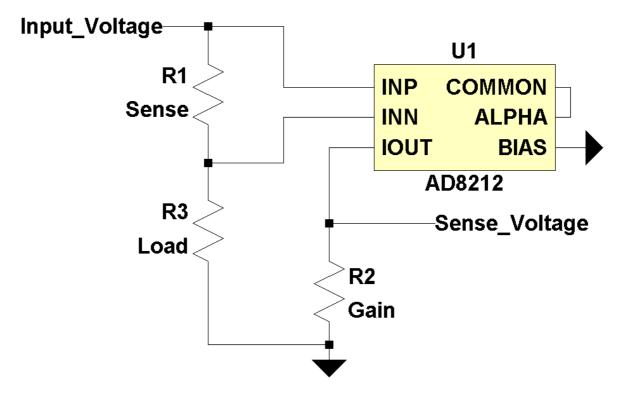

| Circuit Output Voltage (Red)                                                            | 161 |

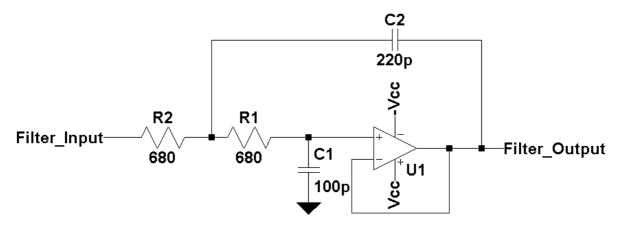

| Fig 173 2MHz Low Pass Sallen Key Anti-Aliasing Filter Circuit                           | 161 |

| Fig 174 Frequency Response of the Anti-Aliasing Filter                                  |     |

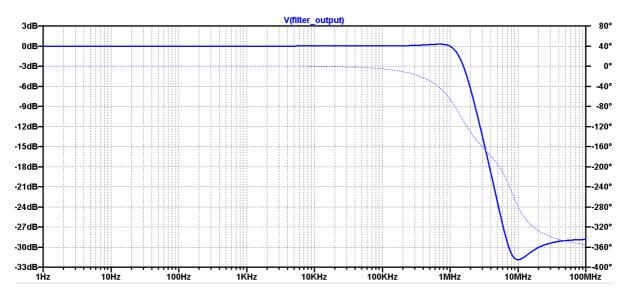

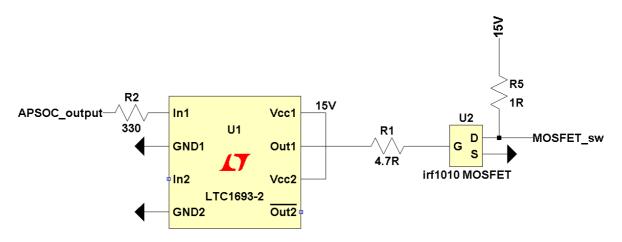

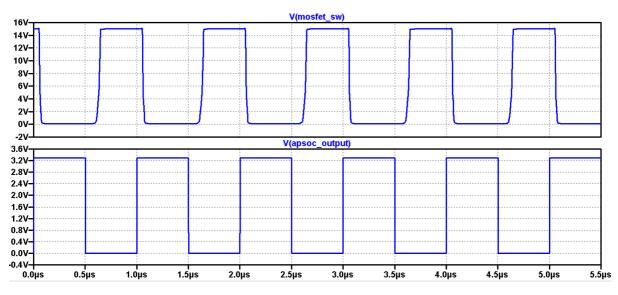

| Fig 175 MOSFET Driver Example Circuit                                                   | 162 |

| Fig 176 MOSFET Driver Circuit Simulation                                                |     |

| Fig 177 Inductor Reference Current being Read from the FPGA Core using the AXI-Lite I   |     |

| с                                                                                       |     |

| Fig 178 CPU Writing Configuration Data into the FPGA Core using the AXI-Lite Bus        | 164 |

| Fig 179 Update of Registers Following Write of Data using AXI-Lite Bus                  |     |

| Fig 180 ANFIS Membership LUT Table Being Written into the FPGA Core from the DMA        |     |

| Core using the AXI-Stream Bus                                                           |     |

| Fig 181 Delta Data for the Inductor Current and Load Current as Transferred over the AX |     |

| Lite Bus Showing the Values being Held for 50 us During a 1A Load Current Decrease      |     |

| Fig 182 Delta Data for the Inductor Current and Load Current as Transferred over the AX |     |

| Lite Bus Showing the Values being Held for 50 us During a 1A Load Current Increase      |     |

| Fig 183 Novel ANFIS Calculation Showing 29 Clock Cycles Between the Start and End       |     |

| Calculation Pulses (in valid and fis valid respectively)                                | 167 |

| Fig 184 Novel ANFIS Calculation Showing 37 Clock Cycles Between the Start and End       |     |

| Calculation Pulses (in_valid and fis_valid respectively)                                | 167 |

| Fig 185 Simulation of the PWM Block with a Fixed 50% Duty Cycle during Soft Start Mod   |     |

| as Controlled by the "fixed_pwm" Signal                                                 |     |

| Fig 186 PWM Simulation with 41.956% Duty Cycle Showing Operation of the MASH            |     |

| Modulator ("duty_ref" Signal)                                                           | 168 |

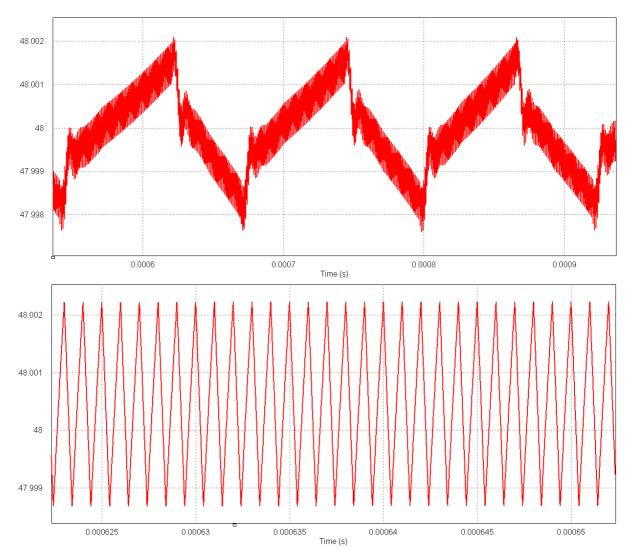

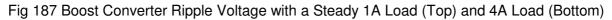

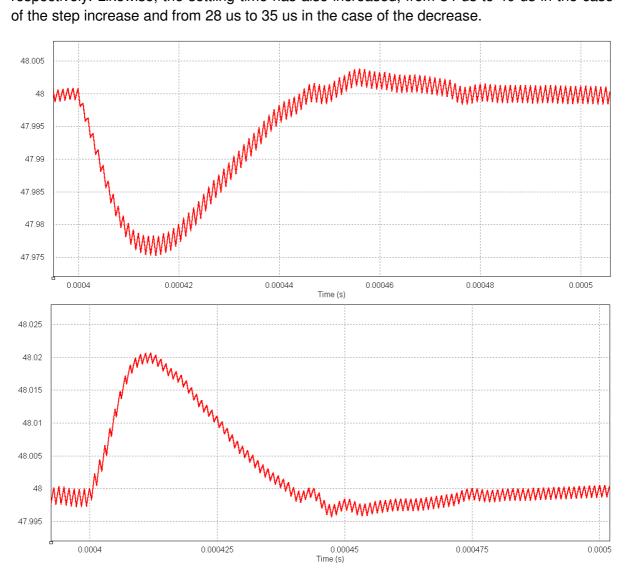

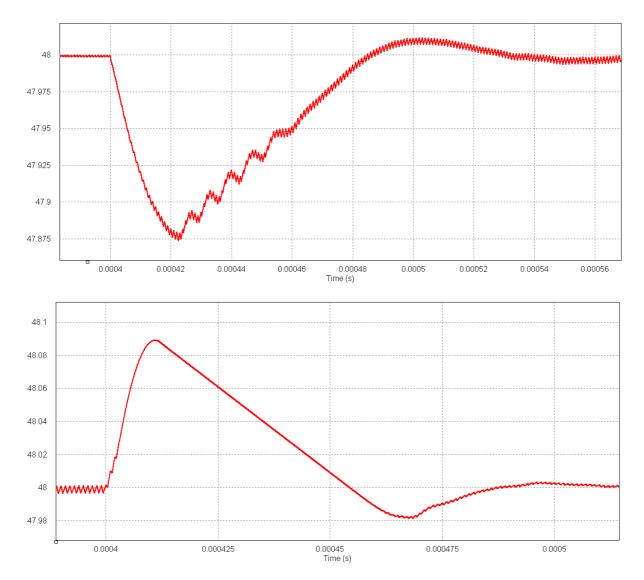

| Fig 187 Boost Converter Ripple Voltage with a Steady 1A Load (Top) and 4A Load (Botto   |     |

|                                                                                         |     |

| Fig 188 Boost Converter Output Voltage with a 1A Decrease in Load Current (Top) and 1  | Α   |

|----------------------------------------------------------------------------------------|-----|

| Decrease in Load Current (Bottom)                                                      | 170 |

| Fig 189 Boost Converter Output with a 1A Increase in Load Current (Top) and 4A Increas | se  |

| in Load Current (Bottom)                                                               | 171 |

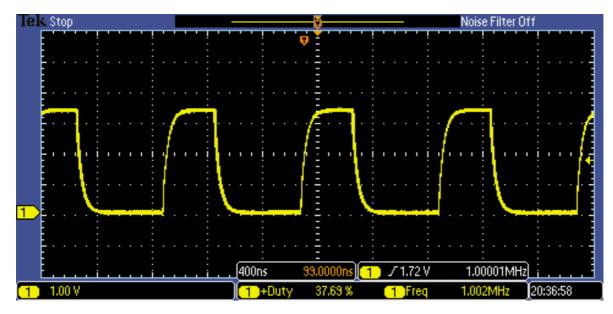

| Fig 190 30VDC Emulated PWM Output with a 37.69% Duty Cycle                             | 173 |

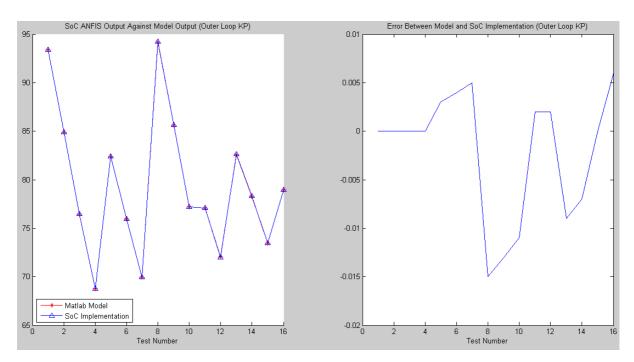

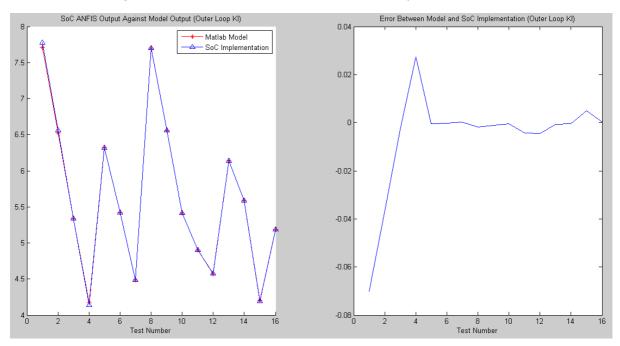

| Fig 191 ANFIS Test Results for the Outer Loop KP Calculator                            | 174 |

| Fig 192 ANFIS Test Results for the Outer Loop KI Calculator                            | 174 |

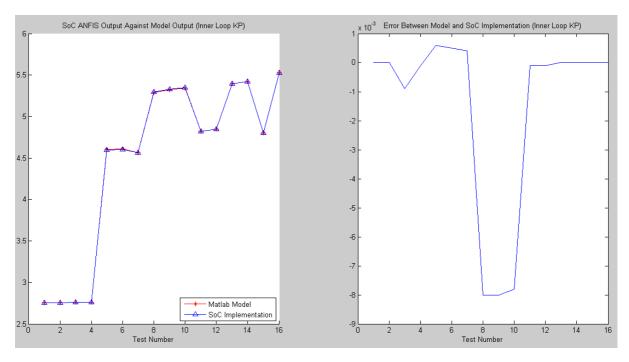

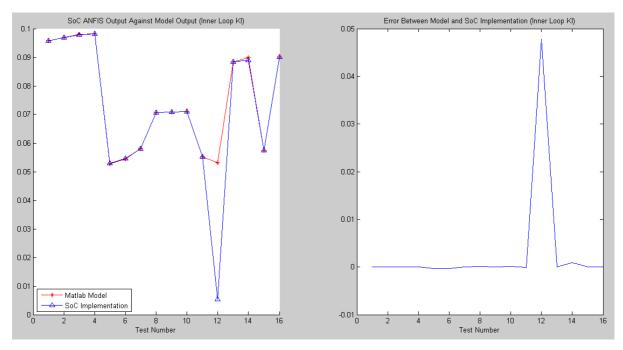

| Fig 193 ANFIS Test Results for the Inner Loop KP Calculator                            | 175 |

| Fig 194 ANFIS Test Results for the Inner Loop KI Calculator                            | 175 |

| Fig 195 Diagram of the System                                                          | 326 |

| Fig 196 Incremental Conductance Algorithm with Variable Step Size                      | 326 |

| Fig 197 ANFIS Network Architecture                                                     | 326 |

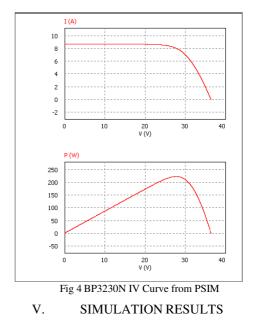

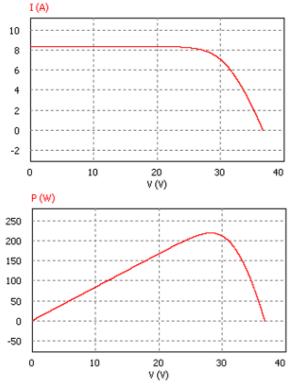

| Fig 198 BP3230N IV Curve obtained in PSim                                              | 326 |

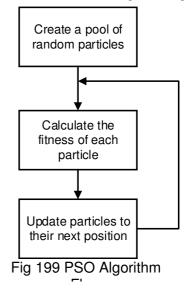

| Fig 199 PSO Algorithm Flow                                                             | 326 |

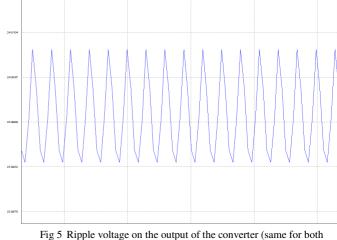

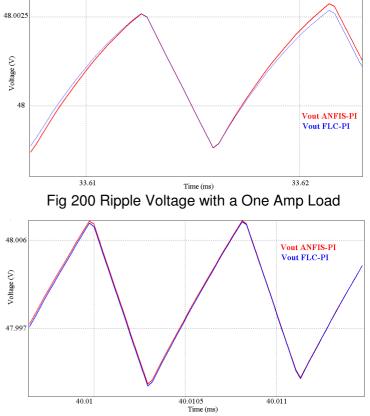

| Fig 200 Ripple Voltage with a One Amp Load                                             | 326 |

| Fig 201 Ripple Voltage with a Four Amp Load                                            | 326 |

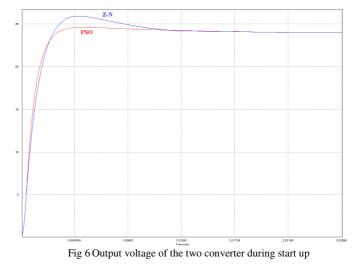

| Fig 202 Boost converter output with a 1A step decrease in current                      | 326 |

| Fig 203 Boost converter output with a 1A step increase in current                      | 326 |

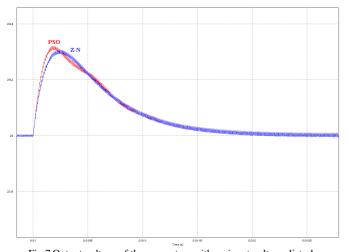

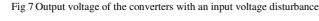

| Fig 204 Boost converter output an input disturbance                                    | 326 |

# List of Tables

| Table 1 Parameter Settings for the Training Algorithm                               | 75  |

|-------------------------------------------------------------------------------------|-----|

| Table 2 48VDC Regulator Steady State Performance Summary                            | 80  |

| Table 3 48VDC Regulator Dynamic Performance Summary                                 | 81  |

| Table 4 Wind Converter Steady-State Performance                                     | 85  |

| Table 5 Wind Converter Dynamic Performance Summary                                  | 87  |

| Table 6 Super Capacitor Parameter Selection Equations (Miller et al (2003))         | 90  |

| Table 7 Super Capacitor Calculated Parameters                                       | 90  |

| Table 8 Super Capacitor Steady-State Performance                                    | 94  |

| Table 9 Super Capacitor Dynamic Performance Summary                                 | 95  |

| Table 10 Battery Discharge Steady-State Performance                                 | 101 |

| Table 11 Battery Dynamic Performance Summary                                        | 102 |

| Table 12 Supercapacitor State Determination                                         | 107 |

| Table 13 Battery State Determination                                                | 107 |

| Table 14 Example of the Sequencer Outputs for a Two Input Five Member ANFIS         | 138 |

| Table 15 Five Input Priority Encoder Logic Table                                    | 139 |

| Table 16 Logic Utilisation for the Different ANFIS Implementation Approaches        | 144 |

| Table 17 PWM Simulation Results                                                     | 150 |

| Table 18 PWM Hardware Test Results                                                  | 150 |

| Table 19 PWM Operation                                                              | 168 |

| Table 20 Comparison between the Original Simulations and the Digital Implementation |     |

| Simulations                                                                         | 172 |

| Table 21 PWM Test Results                                                           | 172 |

# List of Appendices

| Appendix A – PSO Algorithm Script for Matlab                         | 197 |

|----------------------------------------------------------------------|-----|

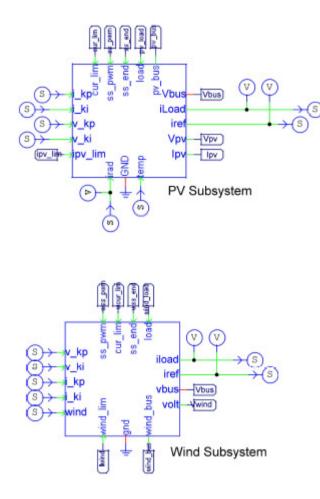

| Appendix B – Psim Schematics for the Hybrid Renewable Energy System  | 202 |

| Appendix B.1 – Top Level Schematic                                   | 202 |

| Appendix B.2 – Solar PV Subsystem Schematic                          | 204 |

| Appendix B.3 – Wind Subsystem Schematic                              | 206 |

| Appendix B.4 – Battery Subsystem                                     | 208 |

| Appendix B.5 – Super Capacitor Subsystem                             |     |

| Appendix C – C Code used in the Hybrid Renewable Energy System Model |     |

| Appendix C.1 – Main.c                                                |     |

| Appendix C.2 - renewable_control.h                                   |     |

| Appendix C.3 – storage_control.h                                     | 223 |

| Appendix C.4 – general_control.h                                     | 228 |

| Appendix C.5 – EMS.h                                                 | 232 |

| Appendix D – FPGA Design Files                                       | 237 |

| Appendix D.1 – der_controller_top.vhd                                | 237 |

| Appendix D.2 – adc_interface.vhd                                     |     |

| Appendix D.3 – xadc_intfc.vhd                                        |     |

| Appendix D.4 – ad7983_intfc.v                                        |     |

| Appendix D.5 – moving_average.vhd                                    | 253 |

| Appendix D.6 – dma_interface.vhd                                     | 255 |

| Appendix D.7 – anfis_ctrl.vhd                                        | 259 |

| Appendix D.8 - single_bit_cdc.vhd                                    |     |

| Appendix D.9 – pulse_cdc.vhd                                         |     |

| Appendix D.10 – anfis_ctrl.vhd                                       | 269 |

| Appendix D.11 – Consequence Parameter LUT Example (pv_vkp_rom.vhd)   | 270 |

| Appendix D.12 – hw_ctrl.vhd                                          | 272 |

| Appendix D.13 – pi_ctrl.vhd                                          |     |

| Appdenx D.14 – pwm_generator.vhd                                     |     |

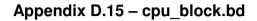

| Appendix D.15 – cpu_block.bd                                         |     |

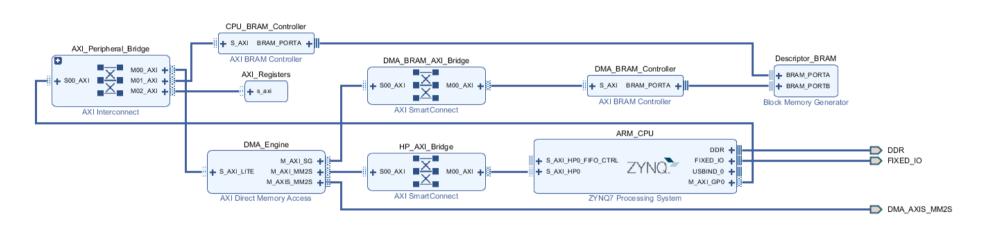

| Appendix D.16 – adc_to_float.bd                                      |     |

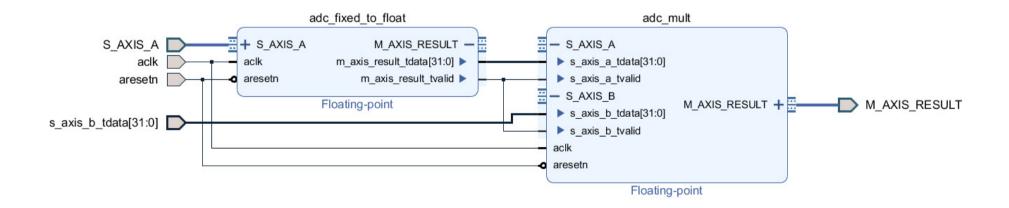

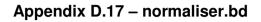

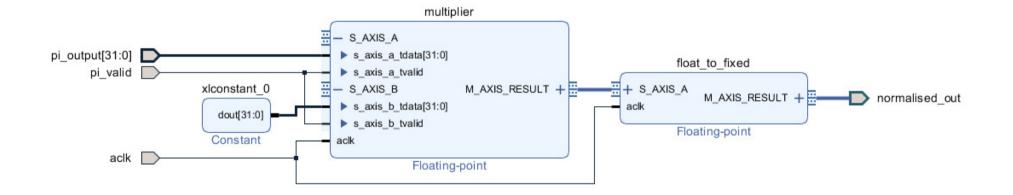

| Appendix D.17 – normaliser.bd                                        |     |

| Appendix E – C Code Used in the CPU Core                             | 290 |

| Append E.1 – Main.c                                                  | 290 |

| Appendix E.2 – AXI_control.h                    | 293 |

|-------------------------------------------------|-----|

| Appendix E.3 – AXI_control.c                    | 294 |

| Appendix E.4 – hw_drivers.h                     | 296 |

| Appendix E.5 – hw_drivers.c                     | 297 |

| Appendix E.6 – hw_test.h                        | 302 |

| Appendix E.7 – hw_test.c                        | 303 |

| Appendix E.8 – member_lut.h                     | 304 |

| Appendix E.9 – member_lut.c                     | 305 |

| Appendix F – APSOC ANFIS Algorithm Test Results | 310 |

| Appendix G – Published Materials                | 325 |

# 1 Introduction

Traditional power generation techniques rely on the burning of natural resources, such as coal or gas, to create kinetic energy which can be transformed into electricity. Using this approach, power can be reliably supplied over a great area using large, centralised power plants. However, in recent decades it has become abundantly clear that the burning of such natural materials is responsible for the release of pollutants into the atmosphere. As the environmental damage caused by these practices has become more apparent, it has become increasingly important for new approaches to be adopted. The use of renewable energy sources, such as solar photovoltaic (PV) cells, wind turbines and hydropower, has become established as a preferred alternative to the traditional generation methods. As a result of this, the popularity of renewable energy sources, such as wind and solar, has increased considerably in the last decade. In order to drive the continued growth of these markets, further technological advances must be made to overcome inherent challenges.

As renewable energy sources rely upon the behaviour of unpredictable natural resources, one major challenge is the reduction of instability which is inherent in power supplies which utilise these technologies. One approach which is becoming increasingly popular is the use of a number of complementary sources and storage devices within a system. This has the effect of improving both the stability and the security of the supply. This methodology requires power to be delivered to a smaller area, with the control becoming decentralised in comparison to the current electrical grid. This decentralised approach, which requires a higher number of distributed power generation stations, is commonly referred to as Distributed Energy Resources (DER).

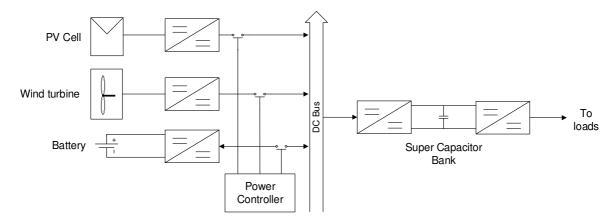

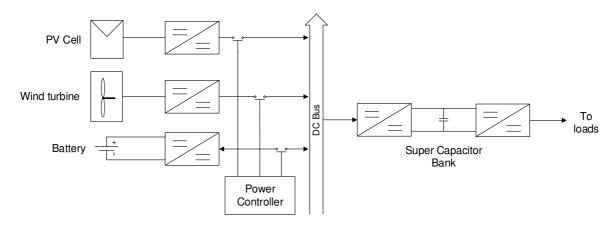

In this research project, a novel approach to the modelling of a DER type system is presented. This system makes use of a solar photovoltaic (PV) cell, a wind turbine and storage elements. This project specifically aims to contribute to the growing research into the control of such systems. In particular, a novel approach to the control of power converters for the renewable energy sources is designed, featuring the use of a new intelligent control solution to improve the performance of the PI algorithm with non-linear plants. The DER model is primarily utilised to demonstrate the capabilities of this novel control approach.

### **1.1 Research Objectives**

This research project has a total of four objectives which are intended to guide the overall aim of initiating a novel control solution which is suitable for use in power converters within DER systems. These objectives relate not only to the creation of the novel control concept but also to the implementation within a hardware device. Each of these objectives is defined in more detail in the rest of this section.

The first objective of this project is the creation of a model for a hybrid renewable energy system using a novel modelling approach. This model encapsulates the behaviour of the power electronics, the renewable energy devices and the control solution. However, this model doesn't consider the transmission lines, the communication buses between the renewable energy converters and the dump load. To meet with this objective, a comprehensive review of the current state of the art is firstly carried out, to ascertain the system topology and an optimal control solution. In order to determine the best methodology for the model of the system, a review of existing modelling solutions is then carried out.

The second objective of this project is the extensive simulation of the system in order to validate its performance. These simulations firstly consider the individual power converters, to demonstrate the characteristics of the novel control solution. A number of realistic use case scenarios can also be created, which are used to demonstrate how the renewable energy sources complement one another in this system. As part of the methodology review carried out for the first objective, suitable modelling tools are selected to streamline this process.

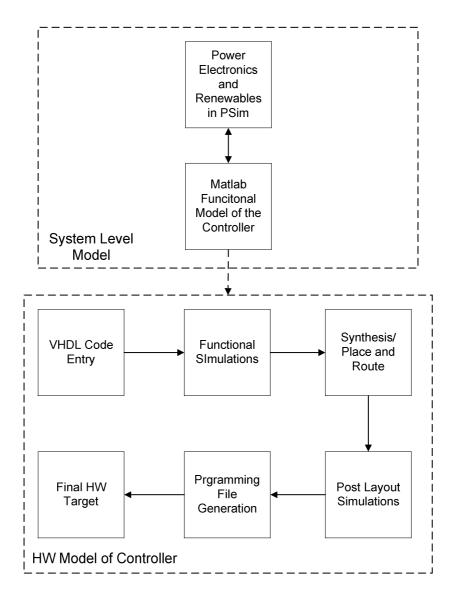

Once the model of the system has been proven at a conceptual level, the next objective is the realisation of the novel aspects of the control solution within a suitable hardware device. An FPGA is chosen as the primary hardware platform for this task, as it offers a high level of parallel processing capabilities. The VHDL modelling language is utilised to create a model of the novel digital controller, which can be used to prove the performance of the design. Using the Vivado design suite, a free EDA tool from Xilinx, this implementation is further analysed to ascertain its temporal performance and logic utilisation requirements.

The final objective of this research project is the validation of the digital controller implementation. This covers simulations of the model, firstly in isolation and then in consideration with the power electronics. Modern co-simulation techniques are utilised as part of this objective, allowing for SPICE based simulations of the power electronics to be carried out in conjunction with the VHDL model. Testing of the real silicon device is also considered as a part of this objective.

### 1.2 Methodology

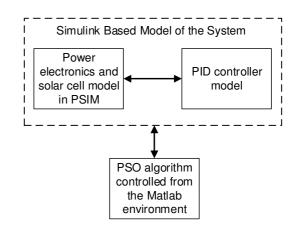

As was discussed in the previous section, the primary objective of this research project is the creation of a novel control solution for power electronic converters. In order to demonstrate the capabilities of this new controller, a DER type system is modelled and simulated. As a part of this work, there are three distinct modelling elements which must be considered – the system level controller, the renewable energy sources and the power electronics. The PSim software tool is used in the modelling of the power electronics and renewable energy sources. This is a specialist tool which is designed to simplify the modelling of power electronics circuits, featuring a number of pre-defined component models. This represents an efficient, rapid prototyping solution for these elements of the system.

The Matlab software tool is utilised as the primary tool in the modelling of the controller, which includes the design of several Artificial Intelligence (AI) based algorithms. This software package is chosen as it includes a number of pre-packaged tools which are intended to simplify the task of designing such algorithms, with the Fuzzy Logic toolbox being one example. In addition to this, Matlab features a powerful yet relatively simple syntax which makes it ideal for the modelling of control algorithms. Using this tool, it is also possible to create a Simulink model which can interface with the PSim software. This allows for co-simulation between the two packages, which helps to optimise the modelling environment.

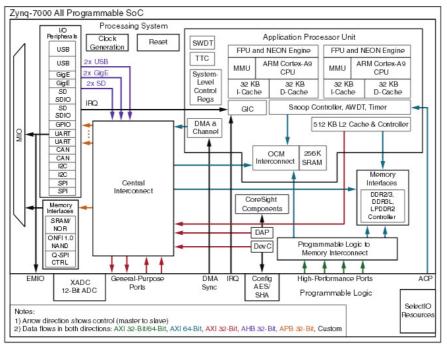

Another objective of this research project is the realisation of the controller algorithms within a suitable hardware device. The Xilinx Zynq All Programmable System-on-Chip (APSOC) is chosen as the final hardware target for this purpose. Therefore, the controller is primarily implemented using VHDL, with the C programming language being used for supporting functionality. In order to model the functionality of the controller, the QuestaSim simulation software is utilised. This is a powerful environment which is designed for the simulation of hardware modelling languages. A key benefit of this is the ability of PSim to interface with this environment, meaning that the power electronics and controller can be considered in a single environment. The synthesis, layout and programming file generation shall be carried out using the Xilinx Vivado tool, which also allows for further analysis of the implementation to be carried out.

### **1.3 Original Contributions**

As part of this research work, there have been a number of original research contributions, some of which have resulted in peer-reviewed publications. These research papers are included in the appendices, whilst their accomplishments are summarised below.

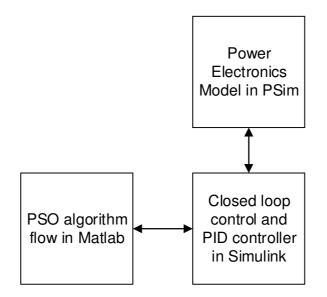

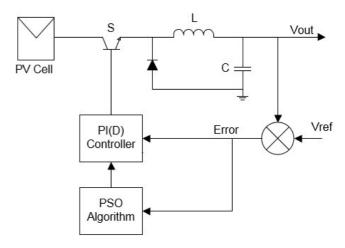

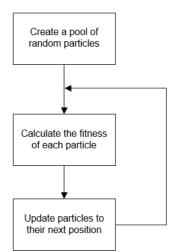

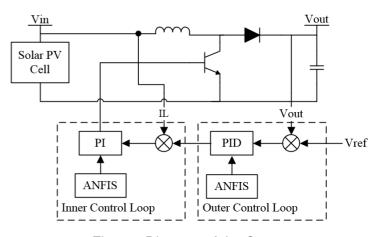

The first original knowledge contribution stems from the use of a new modelling environment for the tuning of PI controllers. This environment utilises co-simulation between PSim and Matlab to create a rapid modelling approach. The research paper which resulted from this work considers the case of a buck converter, fed by a solar PV cell, which is controlled using a PI algorithm. The tuning of the PI controller is carried out using an artificial intelligence based algorithm known as Particle Swarm Optimisation (PSO). The flow of this algorithm is well suited to the Matlab modelling tool, whilst the power electronics and solar PV can be modelled more efficiently using PSim. This paper illustrates how co-simulation between these tools creates a rapid modelling solution for the PSO algorithm.

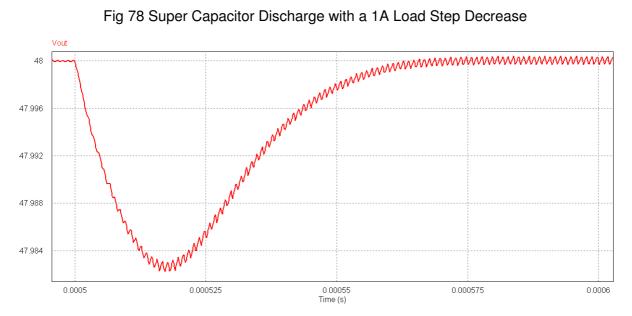

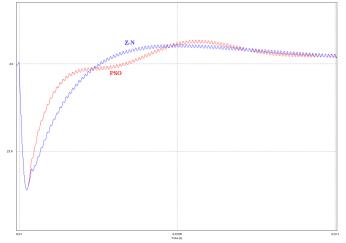

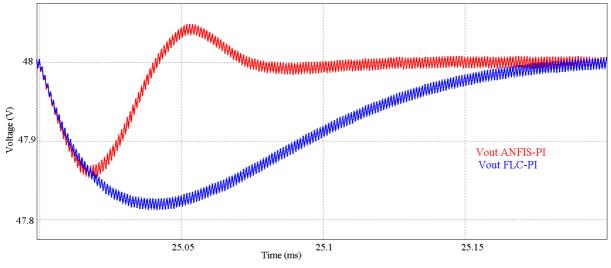

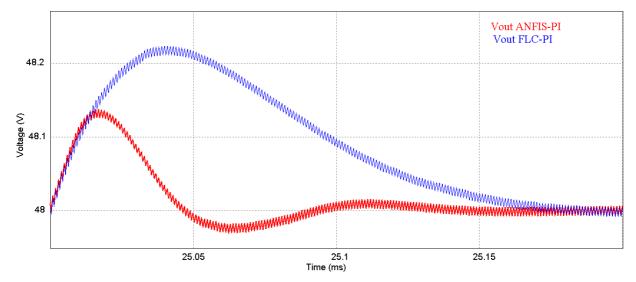

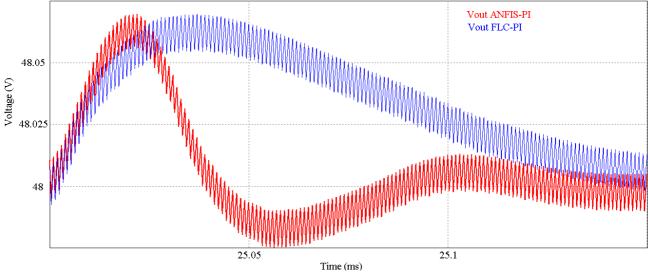

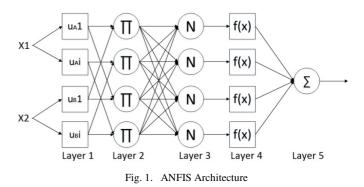

The next original contribution to knowledge is the creation of a novel gain scheduling control solution which is utilised in the power converters. This methodology features the use of a Neuro-Fuzzy control algorithm to provide gain scheduling for a PI-type controller. Adopting this approach improves the performance of the essentially linear PI algorithm with a highly non-linear plant, such as a power converter. The research paper in which this was presented considered a boost type power converter fed by a solar PV cell. Comparisons were made showing how this approach reduces output errors in comparison to a more traditional fuzzy logic based gain scheduling controller.

The final original contribution relates to the implementation of the gain-scheduling controller within an FPGA. Following a review of the existing architectures for the Neuro-Fuzzy algorithm, inefficiencies in the current approaches have been identified. A new architecture has been devised which reduces the calculation time whilst requiring only a small increase in the logical utilisation of the FPGA. The research paper in which this is presented considers a basic use case and makes comparisons with the existing methodology from which it is derived. The paper concludes that the scalability of the architecture is improved, whilst there are a number of simulations presented which demonstrate how the latency of the calculation is greatly reduced.

### **1.4 Structure of the Thesis**

In chapters 2 and 3 of this thesis, detailed background information is introduced for the field of DER systems and control solutions for power converters respectively. As part of this background discussion, a literature review is also presented on both of these topics. In the following chapter, the methodology is presented. This begins with a review of the different modelling tools and hardware solutions which are commonly used before the approach utilised in this project is presented and discussed. The model of the DER system is introduced in chapters 5 and 6, which includes the presentation of a number of simulations to demonstrate the effectiveness of the novel control solution. This begins with a discussion

of the power converters and their individual controllers, in chapter five, before the entire system is considered in chapter 6. The FPGA implementation of the main novel control solution is discussed in detail in chapter 7, including simulation and hardware testing. Finally, chapter 8 demonstrates the behaviour of the FPGA implementation in the context in which it will be utilised. A number of conclusions are then drawn at the end of the thesis, to illustrate how the objectives of the research project have been met and to highlight possible areas of further work.

# 2 Review of Existing Renewable Power System Technologies and Advanced Research Trends

Traditional energy generation schemes rely on the burning of fossil fuels such as coal and gas, an approach which results in the emission of carbon and other pollutants into the atmosphere. As the damage caused by these sources became apparent, a global trend has emerged which seeks to reduce carbon emissions generated from such practices. In the last few years, this has become a headline-grabbing trend thanks to high-profile initiatives such as the Paris climate agreement (Clark and Stothard (2015)). A number of European countries, such as the UK (Pickard and Campbell (2017)), and France (Chrisafis and Vaughan (2017)) have similarly announced an upcoming ban on carbon producing diesel and petrol engines. It seems likely that others, most notably Germany (Briscoe (2017)), will also follow suit shortly. In order to drive this trend, it is obvious that alternative, clean energy sources must be considered. Renewable energy sources, such as wind turbines and solar photovoltaic (PV) cells, are increasingly becoming a preferred alternative to the traditional sources.

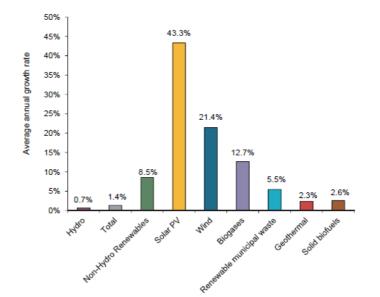

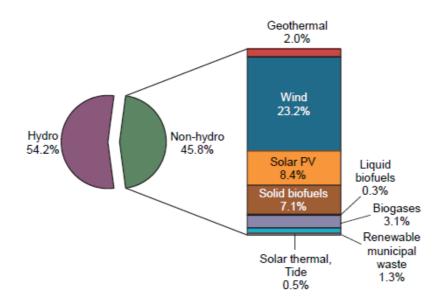

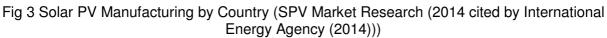

The renewable energy market has enjoyed substantial growth over the last twenty-five years, with energy generation growing at an average of 2.5% in OECD countries, nearly double that of conventional energy generation (1.4%) (International Energy Agency (2017)). This growth rate is especially pronounced in the areas of Solar PV cells and Wind turbines, which have recorded growth rates of 43.3% and 21.4% respectively during this period, as shown in Fig 1. In absolute terms, the total installed power for wind and solar PV increased by 443.1TWh and 35 TWh respectively (International Energy Agency (2017)). Despite this rapid growth in these markets, hydropower continues to be the most widely used renewable energy source, accounting for more than half of renewable energy production as is shown in Fig 2. Hydropower, which is obtained from water energy, is a very well-established method of power production. It has the flexibility to meet with peak supply demands as well as being capable of acting as a storage system, making it a stable source of power. In 2016, the total energy generated by hydropower amounted to 1401.9TWh, compared to 599.4TWh for wind power and 218.3TWh for solar PV power (International Energy Agency (2017)).

Fig 1 Annual Growth Rates of Electricity Production from 1990 to 2016 in OECD Countries (International Energy Agency (2017))

Fig 2 Shares in OECD Renewable Electricity Production for 2016 (International Energy Agency (2017))

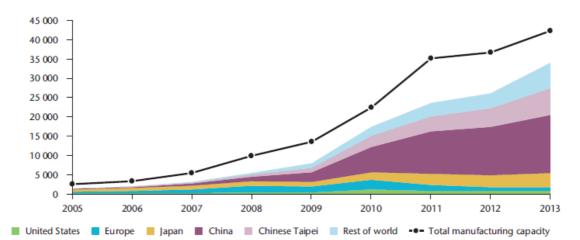

In the last decade, the solar PV market has seen a shift away from Europe and towards China. This has been true not only in consumption terms but also in manufacturing terms, with China supplanting Germany as the largest manufacturer of solar PV modules. Fig 3 shows how production has rapidly increased since 2005 and how the manufacture of modules has shifted towards China, as well as Asia more generally. This shift towards Asian manufacturing bases has helped to reduce production costs, a trend which has been exacerbated by the accompanying increase in manufacturing volume. As a result of this, the installation price for solar PV energy has dropped significantly in the past decade. Mature markets such as Italy and Germany are now price competitive with traditional energy generation (International Energy Agency (2014)). The continuing fall in production prices, combined with strong interest from large industrialising countries such as China and India (International Energy Agency (2016)), means that the solar PV market is forecast to continue its strong growth rates. According to the International Energy Agency (2014), solar PV could potentially account for 16% of global energy production by 2050. This would represent a marked increase from the current market share of less than 10% (International Energy Agency (2014)).

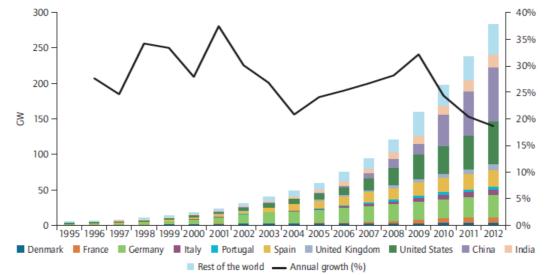

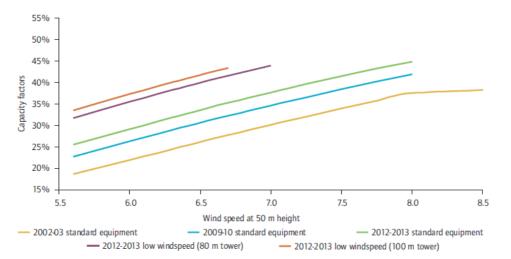

Wind power has seen a similar surge in popularity, with installed capacity more than doubling between 2009 and 2013 (International Energy Agency (2013)). Fig 4 shows how the cumulative installed wind power increased in the period between 1995 and 2012. Wind turbine technology has seen rapid development over the past few years, with improvements in tower height and blade length, in particular, helping to increase their power capacities (International Energy Agency (2013)). Fig 5 shows how the capacity factor of wind turbines increased in the ten years from 2002. This improvement in technology, coupled with falling production costs, means that wind power is becoming increasingly competitive with traditional power sources. In mature markets with good wind resources, such as Brazil, Australia and New Zealand, on-shore wind farms are already cost competitive with newly built power plants (International Energy Agency (2013)). The off-shore market remains less price competitive than the on-shore market, owing largely to the extra complexity of maintenance and installation. According to the International Energy Agency (2013), the wind market is set to continue exhibiting a high growth rate. Forecasts show that by 2050 wind power could be responsible for meeting around 15% of global power demand. This would represent a substantial increase in the current level of around 2.5% as measured in 2013 (International Energy Agency (2013)).

Fig 4 Global Cumulative Growth of Wind Power Capacity (International Energy Agency (2013))

Fig 5 Capacity Factor History of Selected Wind Turbines (Wiser and Bolinger (2013))

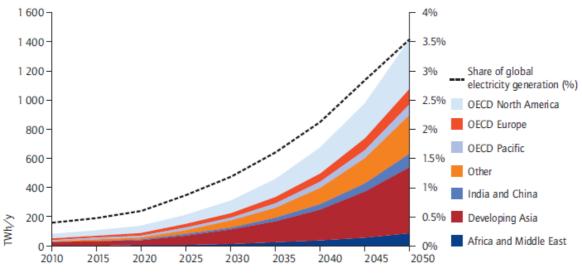

Whilst not as popular as the more mature renewable energy technologies, there is still a market for bioenergy and geothermal power. Bioenergy focuses on the creation of biomass materials, which can support the use of coal in traditional power plants. The co-firing of turbines using a mix of coal and biomass is the most cost-efficient way of producing electricity from biomaterials. This stems largely from the fact there is no need to invest in new equipment and existing infrastructure, as traditional power plants are sufficient for the deployment of bioenergy. As well as the co-firing method, which has limitations on the amount of biofuel that can be used, there are a number of other methods which are being developed. However, none of these systems are currently widely deployed. There has been considerable growth in bioenergy take up since 1991, with output more than doubling up to 2009 to contribute around 1.24% (Brown, Muller and Dobrotkova, 2011) of the world energy supply. Geothermal power relies on the earth's heat, estimated to be 5,500°C, to produce energy. This heat is generally drawn from naturally occurring sources - hydrothermal (volcanic) resources, gaps in the Teutonic plate and hot rock. Whilst the required volcanic resources are limited by location, it is possible to use hot rock in all locations. These hot rocks can be used to produce steam, which in turn is used in steam-based generators. It is anticipated by the International Energy Agency (2011) that the market for geothermal power will show robust growth over the coming decades, with forecasts suggesting it could account for 3.5% of global power by 2050 compared to less than 1% now, as shown in Fig 6.

Fig 6 Forecast Growth in Geothermal Power Production by Region (International Energy Agency (2011))

Despite the high growth rates for wind and solar energy, there still remain a number of challenges which need to be overcome to continue to drive this development. Price remains perhaps the main barrier for mass penetration, although the International Energy Agency (2016) anticipates that by 2040 most renewable energy will be price competitive without subsidies. There are also a number of technical challenges which must be overcome, particularly within the manufacturing and technologies for new sources. Work is being done in improving the efficiency of currently expensive manufacturing processes, such as PV cell fabrication and large wind turbine construction, which will be essential in ensuring that the popularity of renewable energy continues to increase.

One major technical challenge with renewable systems is controlling the inherently unstable nature of power supplies, which rely on unpredictable natural resources. One solution to this

problem that has gained popularity is the use of a number of complementary sources together, such as wind generators and solar PV cells, which help to smooth fluctuations in the supply. Using this methodology, the energy system will provide power to a smaller area and the control will consequently become decentralised, an approach known as distributed energy resources (DER). Although the idea behind DER systems is well established, there is still a need for enhancements to be made before the use on a large scale becomes a reality. A major area which needs improvement is the control of such a system, which must be able to produce a stable and secure supply, which meets the tight power quality needs of the grid.

In this section, a review is conducted into the major technologies involved in the development of a new DER concept. This starts with the consideration and review of the renewable power generation technologies and then also considers power converters, which form a key part of the system. Finally, a review is conducted into the current research being done in relation to renewable energy systems and power converter technology.

### 2.1 Renewable Energy Sources and Technologies Employed

There are a number of different technologies used in the generation of power from renewable sources, covering aspects of mechanical, electrical and electronic engineering. In this section, some of the key energy sources and technologies are introduced.

### 2.1.1 Wind Systems

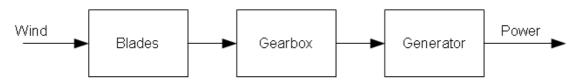

The potential for wind energy is vast, with the relative maturity of the technology meaning they are already a popular renewable energy source. Conversion of wind power into mechanical motion is a centuries-old concept, dating back to the use of windmills for the grinding of wheat. Although modern wind machines are much more sophisticated, with larger and more aerodynamic blades, this same basic mechanical principle is at the heart of the modern wind turbine. When wind comes into contact with the large blades of a wind turbine, the wind power forces the turbine to rotate, with the rate of rotation being proportional to the speed of the wind. This motion is then carried through to the generator, via a gearbox, where it forces the rotor into motion and thus starts to produce power. A typical block diagram for a wind turbine system is shown in Fig 7.

Fig 7 Wind turbine block diagram

The blades play a critical role in the wind turbine system as they are the primary component in converting the potential energy of the wind into rotating mechanical motion which can be used by the generator. As a result of this, the blades play a big role in the efficiency of the system and their design is critical to the performance. In order to achieve greater efficiency, there are three key considerations - size, number of blades and aerodynamics. The size of the blade, or rather the length, dictates how much wind will come into contact with the blade. This means that bigger blades are better, as more energy hitting the blades equates to greater energy production. Similarly, better aerodynamics allows for higher rotational speed which again results in higher power generation. The aerodynamics of the blades have received much attention and modern blades now closely resemble the construction of aeroplane wings, featuring aerofoil type shapes to reduce drag and maximize lift as far as possible. The number of blades is actually limited by other factors as it becomes increasingly difficult to produce aerodynamically efficient blades which are adequately large and robust as more are added to a turbine. Therefore, the best balance has been found with three blades per turbine.

Electrically speaking, the generator is the core component of the wind turbine system as this is where the potential of the mechanical energy is transformed into electrical energy. There are a number of different generators which can be used in a wind system but the most commonly used types are permanent magnet synchronous machines (PMSM) and induction generators. DC generators are also used occasionally, especially to integrate with DC systems such as those which are employed with PV cells, but they generally require much higher revolution speeds to generate power. Due to this inefficiency, it is more common and practical to use an AC generator with a power converter to achieve DC from the wind turbine.

The induction generator is popular for use in wind turbines due to its ability to produce power at a range of frequencies. The stator of the induction generator is constructed from slotted iron cores, with wires being wound into the slots to form the electromagnet. The rotor is made up of cylindrical conductive bars evenly spaced around the periphery. In order to produce power, the speed of the rotor must be greater than the stator's synchronous speed, which is dictated by the frequency of the stator's AC supply. The induction generator is a fairly simple form of generator and is therefore relatively simple to control, as well as being rugged and inexpensive. All of these factors contribute to their ongoing popularity in wind turbines.

The key defining feature of PMSM generators is the presence of permanent magnets in the construction rather than the use of an electromagnet, as is required in most generator technologies. In a PMSM generator, the stator is again constructed from a core which features a number of windings, whilst the rotor features fixed permanent magnets. The operation of the generator is fairly simple, with the rotation of the rotor mounted magnets creating an electromagnetic field in the stator. This, in turn, generates an electrical output through electromagnetic induction. PMSM generators are a popular choice of generator in wind turbine systems, largely owing to the fact they require no excitation or gearbox meaning they are simple to integrate. The main disadvantage of these devices is that the magnetic flux density of permanent magnets is less than that of electromagnets, effectively limiting the power capabilities. In addition to this, they also tend to be more expensive than other generator technologies.

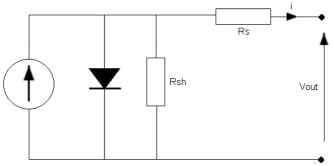

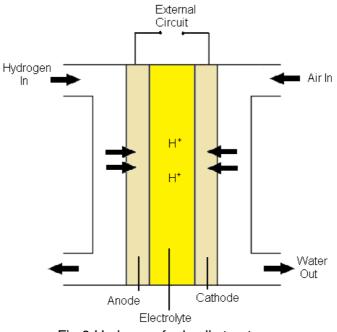

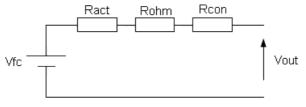

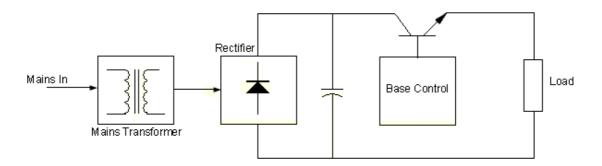

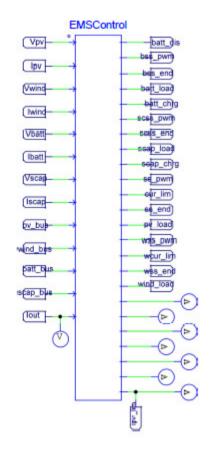

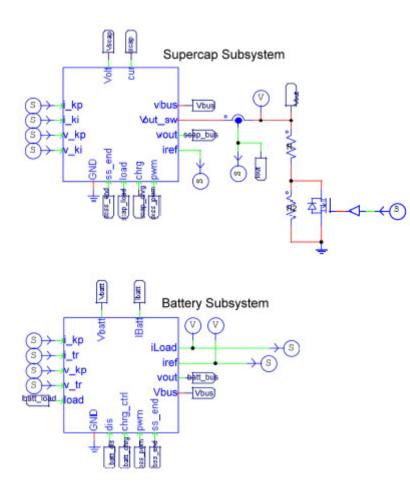

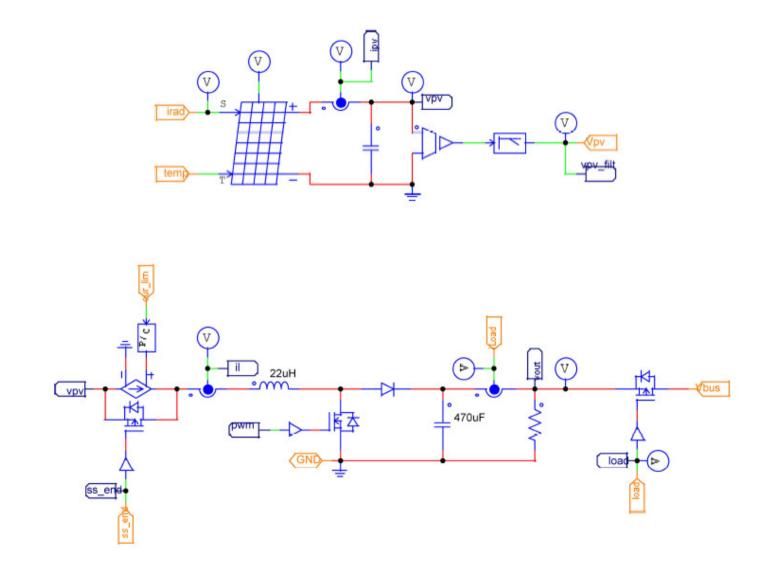

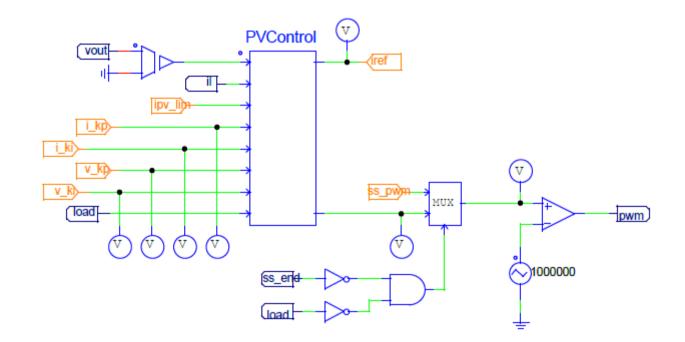

### 2.1.2 PV Systems