# An Improved FPGA Implementation of Direct Torque Control for Induction Machines

Tole Sutikno, *Member, IEEE*, Nik Rumzi Nik Idris, *Senior Member, IEEE*, Auzani Jidin, *Member, IEEE*, and Marcian N. Cirstea, *Senior Member, IEEE*

Abstract—This paper presents a novel direct torque control (DTC) approach for induction machines, based on an improved torque and stator flux estimator and its implementation using Field Programmable Gate Arrays (FPGA). The DTC performance is significantly improved by the use of FPGA, which can execute the DTC algorithm at higher sampling frequency. This leads to the reduction of the torque ripple and improved flux and torque estimations. The main achievements are: i) calculating a discrete integration operation of stator flux using backward Euler approach, ii) modifying a so called non-restoring method in calculating the complicated square root operation in stator flux estimator, iii) introducing a new flux sector determination method, iv) increasing the sampling frequency to 200kHz such that the digital computation will perform similar to that of the analog operation, and v) using two's complement fixed-point format approach to minimize calculation errors and the hardware resource usage in all operations. The design was achieved in VHDL, based on a Matlab/Simulink simulation model. The Hardware-In-the-Loop (HIL) method is used to verify the functionality of the FPGA estimator. The simulation results are validated experimentally. Thus, it is demonstrated that FPGA implementation of DTC drives can achieve excellent performance at high sampling frequency.

Index Terms—Direct Torque Control, Field Programmable Gate Arrays, Induction Machine, VHDL

#### I. INTRODUCTION

DIRECT Torque Control (DTC) of machine drives has gained popularity since it can provide fast instantaneous torque control with simple control structure. The original DTC scheme was proposed by Takahashi in 1986 [1] and uses hysteresis controllers to control independently both the stator flux and the torque. Ideally, the error or ripple of the torque (or flux) is restricted within the hysteresis band, so that the output torque (or flux) will satisfy its demand. However, in practice, as the hysteresis controller follows a discrete

Manuscript received December 15, 2011. This work was supported in part by the Universiti Teknologi Malaysia under Grant VOT 78584.

- T. Sutikno is with the Electrical Engineering Department, Universitas Ahmad Dahlan, Yogyakarta, Indonesia. He is currently pursuing for his PhD at Universiti Teknologi Malaysia. (email: tole@ee.uad.ac.id).

- N. R. N. Idris is with the Energy Conversion Department, Universiti Teknologi Malaysia (UTM), Johor, Malaysia (corresponding author, phone: 60-755-36139; fax: 60-755-66272; e-mail: nikrumzi@ieee.org).

- A. Jidin is with the Power Electronics and Drives Department, Universiti Teknikal Malaysia Melaka, Melaka, Malaysia (e-mail: auzani@ieee.org).

- M. Cirstea is with the Computing and Technology Department, Anglia Ruskin University, Cambridge, UK (e-mail: marcian@ieee.org).

computation approach, this is impossible to achieve due to the delay between the torque sampling instant and the instant the corresponding switching status is passed to the inverter [2]. The ripple might exceed beyond the hysteresis bands, and hence tends to select the reverse voltage vector that causes rapid increase/decrease of the torque [3]. This, consequently, will produce larger torque ripples and slightly degrade the performance of DTC. Several methods were proposed to minimize the output torque ripple. These include the use of space vector modulation (SVM) [4-7], the injection of dithering signal [8], the use of constant carrier frequency [3] and recently, the hysteresis based DTC with predictive control [9-12]. All these methods require knowledge modifications of machine parameters which will complicate the simple DTC structure and will increase its control sensitivity. Moreover, the same effectiveness in minimizing the output torque ripple using those methods can be achieved if a higher switching frequency is applied, with a high speed processor.

Traditionally, the DTC algorithm is executed using a Digital Signal Processor (DSP) [13-15], with code written using C-programming or a graphical programming approach, a much simpler method, appropriate for rapid prototyping. It should be noted that the sampling frequency of the processor depends on the computational burden. For the basic DTC algorithm, normally the sampling frequency of the DSP (e.g. DSPACE 1104 or TMS C2000 series) can reach up to 20 kHz. This, however, is still insufficient to operate the discrete hysteresis controller, similar to that of analog/continuous hysteresis system, so that the output torque ripple can be restricted within the band, even when it operates at the worst conditions (i.e. at very low speeds that cause extreme torque slope).

Some works used a combination of DSP and Field Programmable Gate Arrays (FPGA), reducing DSP's computational burden by distributing some DTC algorithm tasks (look-up table, blanking time generator and hysteresis controllers) to the FPGA. Thus, the sampling period to execute the overall DTC algorithms can be minimized to the output torque ripple [16-18]. However, the combination of controllers increases the cost and complexity of the interfacing circuit, and is not a practical solution for commercialization purposes. Some attempts [19-20] implemented entire DTC algorithms on a single FPGA but the HD coding there was generated using third party packages, i.e. MATLAB/Simulink, with the Xilinx System Generator Fixed-point toolbox, which is not fully

optimized to achieve fast sampling frequency. Work [20] reports significant max. sampling frequency improvement to twice of that obtained with a DSP (which is 40 kHz).

This paper presents an effective way to design, simulate and implement the flux and torque estimations for hysteresis-based DTC utilizing FPGAs. The main contribution of this paper is the development of the flux and torque estimators using VHDL code on the FPGA (i.e. from scratch), the code being optimized to achieve a sampling frequency of 200 kHz. With the highest sampling frequency, it is therefore possible for the torque ripple to be restricted within its hysteresis band and hence minimize the ripple by reducing the band size. Moreover, the performance of flux estimation as well as the inherent current control in DTC system can be improved. Taking this into account, the estimations in DTC are the main parts to be implemented using FPGA, as they involve complex calculations (e.g. integrals, square-root, multiplication and precise current scaling factor). The optimized VHDL code design will be based on the MATLAB simulation model, where the type of data, number of bits (resolution), sampling time, scaling factor performed in simulation are similar to that of FPGA implementation. The estimations of stator flux and torque in the DTC of the induction machine will be presented in Section II. The equations of stator flux and torque in discrete form and sector identification will be given in Section III. Section IV will present the description of the estimations using MATLAB simulation and Modelsim Altera simulation. Finally, the simulation and experimental results are compared, to verify code/design effectiveness at the highest sampling frequency.

#### II. MAJOR PROBLEM IN HYSTERESIS-BASED DTC

Despite its simplicity, the DTC based on hysteresis controller causes some major problems such as variable inverter switching frequency, high torque ripple and high sampling requirement for digital implementation [3-8]. These problems are briefly described as follows.

# A. Variable inverter switching frequency

In hysteresis-based DTC, the switching frequency of a VSI is mainly governed by the switching of the torque hysteresis comparator. The slope of the torque waveform, which directly affects the switching of the hysteresis comparator, vary with the operating conditions (rotor speed, stator and rotor fluxes, DC link voltage) [5]. This can be seen from the discrete form of the torque equation given by (1):

Torque slope =

$$\frac{T_{e,n+1} - T_{e,n}}{\Delta t} = -T_{e,n} \left( \frac{1}{\sigma \tau_s} + \frac{1}{\sigma \tau_r} \right) + \frac{3}{2} P \frac{L_m}{\sigma L_s L_r} \left[ \left( v_{s,n} - j\omega_r \varphi_{s,n} \right) \bullet j \varphi_{r,n} \right]$$

(1)

where:

$\phi_s\ :\ stator\ flux\ linkage\ space\ vectors\ in\ stationary\ reference\ frame$

Φ<sub>r</sub> : rotor flux linkage space vectors in stationary reference frame

: rotor electrical speed in rad/s

s : stator voltage space vector in stationary reference frame

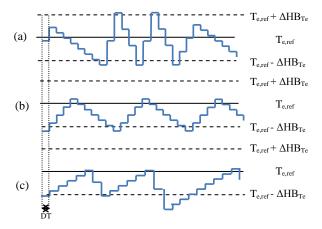

Fig. 1. The waveforms of output torque sampled at DT in the hysteresis comparator for (a) low speed, (b) middle speed and (c) high speed

To illustrate this, waveforms of discretized electromagnetic torque under 3 different steady-state operating conditions are shown in Fig. 1. These are drawn so that only the effects of motor speed and the applied voltage are considered. During the positive torque slope, the active voltage vector is applied; otherwise, the zero voltage vector is selected. It can be noticed that the torque slopes (for positive and negative slopes) vary with the operating speed. As a result, the torque switching frequency and hence the VSI switching frequency also vary with operating conditions. Thus, it is common practice to select the device with switching capability based on the worst case of operating conditions.

#### B. High torque ripple

In digital implementation, the output torque is calculated, and the appropriate switching states are determined at fixed sampling time (DT in Fig. 1). This, however, causes a delay between the instant the variables are sampled and the instant in which the corresponding switching status is passed to the inverter, therefore, the torque ripple cannot be restricted exactly within the hysteresis band. If the band is set to be too small, the overshoot of the torque beyond the hysteresis band could cause a reverse active voltage vector selection, instead of a zero voltage vector selection. The selection of the reverse voltage vector causes the torque to decrease rapidly and as a result the torque ripple increases [8, 18, 21-24]. This situation is illustrated in Fig. 1(a).

#### C. The need for high speed processor

Reducing torque ripple by lowering the band width of hysteresis comparator would be fruitless when the processor used has a limited sampling frequency. All the constraints which have been mentioned above can be eliminated if a high-speed processor is utilized, where the discrete hysteresis controller performs closer to the operation of an analog based comparator. As shown in Fig. 1(a) and discussed in sub-

section B, the rapid decrease of torque due to the selection of reverse voltage vector can be avoided if the sampling time (DT) is sufficiently reduced.

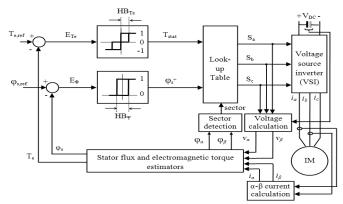

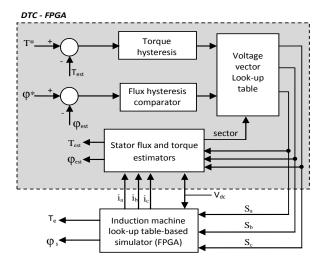

#### III. PROPOSED DIRECT TORQUE CONTROL

Fig. 2 shows a simple structure of hysteresis-based DTC by Takahashi [1]. A decoupled control of torque and flux was established to permit fast instantaneous control. The stator flux is controlled using a 2-level hysteresis comparator, while the electromagnetic torque is controlled using a 3-level hysteresis comparator. The outputs of the comparators, along with sector flux information, are used to index the look-up Table, to select the appropriate voltage vectors to control simultaneously both the stator flux and the torque. The most significant element that can guarantee a satisfactory DTC performance is the estimation of the stator flux and the torque.

In order to estimate the stator flux and the electromagnetic torque, several parameters need to be determined. The mathematical model to be used is tailored to the needs of controlled drives [25]. Firstly, the stator currents from the motor  $I_a$  and  $I_b$ , are transformed into  $\alpha$ - $\beta$  coordinates [26], which are adequately suited to the DTC algorithm, as follows:

$$I_{\alpha} = I_{\alpha} \tag{2}$$

$$I_{\beta} = \frac{\sqrt{3}}{3} (I_a + 2I_b) \tag{3}$$

At the same time, by using the switching status ( $S_a$ ,  $S_b$  and  $S_c$ ) produced by the switching table, the stator voltages in the  $\alpha$ - $\beta$  reference frame are determined:

$$V_{\alpha} = \frac{V_{dc}}{3} (2S_a - S_b - S_c) \tag{4}$$

$$V_{\beta} = \frac{\sqrt{3}}{3} V_{dc} (S_b - S_c) \tag{5}$$

Then, using the calculated  $I_{\alpha}$ ,  $I_{\beta}$ ,  $V_{\alpha}$  and  $V_{\beta}$ , the estimation of the stator flux in  $\alpha$ - $\beta$  coordinates is performed as follows:

$$\varphi_{\alpha} = \varphi_{\alpha_{\alpha b l}} + (V_{\alpha} - R_{S} I_{\alpha}) T_{S}$$

(6)

$$\varphi_{\beta} = \varphi_{\beta_{cl}} + (V_{\beta} - R_{S}I_{\beta})T_{s} \tag{7}$$

Finally, equation (8) calculates the flux magnitude by using a square root calculation, whereas the electromagnetic torque is estimated through equation (9).

$$\varphi_{s} = \sqrt{\varphi_{\alpha}^{2} + \varphi_{\beta}^{2}} \tag{8}$$

$$T_e = \frac{3}{4} P(I_\beta \varphi_\alpha - I_\alpha \varphi_\beta) \tag{9}$$

The original scheme is based on hysteresis controllers, where the output status from the controllers, together with the sector flux information, are used to select the optimized voltage vectors from the look-up table to satisfy simultaneously both flux and torque references. The flux vector is controlled to form a circular flux shape.

Fig. 2. Control structure of DTC based induction machine

# IV. DESIGN OF TORQUE AND STATOR FLUX ESTIMATOR

# A. Proposed Method to Improve Torque and Stator Flux Estimator

This paper presents an improved FPGA-based torque and stator flux estimator for DTC induction motor drives, which permits very fast calculations. The improvements are performed by: i) calculation of the discrete integration operation of the stator flux using backward Euler approach; ii) reducing the sampling time down to 5µs; to avoid saturation due to DC offset present in the sensed currents, the LPF Filter is applied; iii) modifying the non-restoring method to calculate complicated square root operation of the stator flux; iv) introducing a new sector judgment method. In all operations of FPGA implementation, the two's complement fixed-point format approach is used in order to minimize calculation errors and the hardware resources usage.

#### 1. Fixed-point Arithmetic

A fixed-point variable consists of a binary pattern which is encoded in two's complement number, and a binary point. It is a way to encode negative numbers into ordinary binary. The size of the binary pattern and the location of the binary point are specified using three parameters, namely: sign bit, integer word length (IWL) and fraction word length (FWL). The total number of binary pattern bits is well-known as word length (WL). The approach can represent numbers in the range [-2<sup>IWL</sup>, 2<sup>IWL</sup>] with a step size of 2<sup>-FWL</sup>. When using this arithmetic, the most important aspect is always to consider the binary point location for every variable. VHDL has supported the fixed-point arithmetic operations, and designers have some manipulation flexibility to improve performance.

## 2. Backward Euler Approach

The discrete backward Euler formula is y(n) = y(n-1) + kT.u(n). It is simpler for FPGA hardware implementation, comparing to the forward Euler and Trapezoidal method in that they require the register to store the previous value of u(n-1) function. The backward Euler integration method also can to maintain the system stability in the large step size. Therefore, the discrete backward Euler integration method is chosen to calculate the quadrature flux  $(\varphi_{\alpha}$  and  $\varphi_{\beta}$ ).

#### 3. LP Filter

Notice that Rs is the estimated stator resistance, while Ts is the implementation sampling time. Works [27-28] suggested that a filter should be added to the integrator in the practical implementation to avoid integration drift problem due to the DC offset in the sensed currents. The stator flux equations are:

$$\varphi_{\alpha} = (\varphi_{\alpha_{\alpha M}} + (V_{\alpha} - R_{S}I_{\alpha})T_{s})(I - \omega_{c} * T_{s})$$

$$\tag{10}$$

$$\varphi_{\beta} = (\varphi_{\beta_{old}} + (V_{\beta} - R_{S}I_{\beta})T_{s})(I - \omega_{c} * T_{s})$$

$$(11)$$

#### 4. Non-restoring Square Root Algorithm

In DTC drives, the stator flux ( $\varphi_s$ ) is calculated as square root of the quadrature flux magnitude. To calculate the stator flux ( $\varphi_s$ ), the non-restoring square root algorithm, proposed by [29], is modified as below (D=radicand, q=quotient, r=remainder, and n=half of the radicand word size):

$$\begin{split} r_0 &= -1 & (\frac{n}{2} + 2bits) \\ q_0 &= 0 & (\frac{n}{2} + 1bits) \\ For i &= 0 \text{ to } n\text{-}1 \text{ do:} \\ If \ r_i &\geq 0 \ \text{ then} \\ r_{i+1} &= \left(4r_i + D_{(n-2i)-1}D_{(n-2i)-2}\right) - (4qi+1) \\ else \\ r_{i+1} &= \left(4r_i + D_{(n-2i)-1}D_{(n-2i)-2}\right) + (4qi+3) \\ If \ r_{i+1} &\geq 0 \\ q_{i+1} &= 2q_i + 1 \\ else \\ q_{i+1} &= 2q_i \end{split}$$

The square root result is  $q_n(\frac{n}{2} - 1 \text{ downto } 0)$ , coded in  $\frac{n}{2}$  bits.

#### 5. New Sector Identification

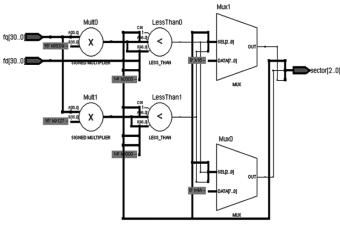

The present work has created a simpler method to analyze the sectors of the voltage vector, based on a comparison between  $\varphi_{\beta}$ ,  $\sqrt{3}\varphi_{\alpha}$ ,  $-\sqrt{3}\varphi_{\alpha}$  and 0, which is modified from [30]. With the comparison, it is simpler to determine the sector of the voltage vector, compared to the conventional methods of using arc tan of angle, three stages comparison based on  $\varphi_{\alpha}$ ,  $\varphi_{\beta}$  or determination of angle using CORDIC algorithm [31]. The proposed method is single stage, based on the fact that three comparisons are performed in parallel, without angle calculation, so that faster computation is achieved and less incorrect voltage vector selections. Table I shows the Karnaugh map of the proposed sector identification.

TABLE I

KARNAUGH MAP OF THE PROPOSED SIMPLER IDENTIFICATION OF

| THE SECTORS            |                                              |                                               |          |  |

|------------------------|----------------------------------------------|-----------------------------------------------|----------|--|

| INPUT                  |                                              |                                               | OUTPUT   |  |

| $\varphi_{\alpha} > 0$ | $\varphi_{\alpha} > \sqrt{3}\varphi_{\beta}$ | $\varphi_{\alpha} > -\sqrt{3}\varphi_{\beta}$ | (sector) |  |

| 0                      | 0                                            | 0                                             | 101      |  |

| 0                      | 1                                            | 0                                             | 110      |  |

| 0                      | 0                                            | 1                                             | 100      |  |

| 0                      | 1                                            | 1                                             | ddd      |  |

| 1                      | 0                                            | 0                                             | ddd      |  |

| 1                      | 1                                            | 0                                             | 001      |  |

| 1                      | 0                                            | 1                                             | 011      |  |

| 1                      | 1                                            | 1                                             | 010      |  |

Through the simplification, it will be possible to get simpler logic of the sector analysis for FPGA implementation through VHDL gate level coding; each sector is represented on 3-bits.

#### B. The Design Flow

The validation of the designed torque and flux estimators was performed by using the Hardware-in-the-Loop (HiL) method. The DTC MATLAB/Simulink model was simulated and then, the same data  $I_a$ ,  $I_b$ ,  $S_a$ ,  $S_b$ , and  $S_c$  used for the simulation, was copied from the MATLAB workspace to VHDL codes, along with the inputs for the targeted FPGA. The VHDL codes were simulated in ModelSim-Altera before being synthesized and implemented in FPGA.

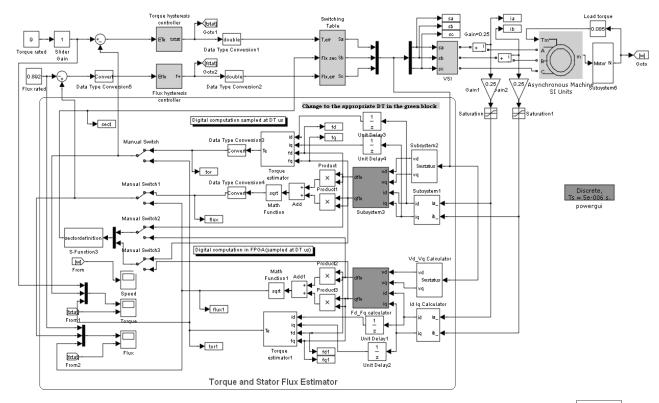

#### V. MATLAB AND MODELSIM-ALTERA SIMULATIONS

In order to verify the torque and stator flux estimator models, a comprehensive DTC simulation was conducted. in Matlab/Simulink (Fig. 3). The upper model is a standard model (which is not ready yet to be implemented in FPGA) and the lower model is generated as one ready to be implemented in FPGA. The simulations of the DTC model, which perform double-precision calculations, are used as references to digital computations executed in FPGA implementation.

The standard Simulink models are not ready as direct FPGA design input, , the designer must prepare them, as the FPGA programming will be conducted in two's complement. In principle, the procedure is similar with the one in [19, 32], which is aimed to use a minimum number of operators that process a maximum number of operations.

The DTC model was simulated in Matlab/Simulink and then the same data (I<sub>a</sub>, I<sub>b</sub>, S<sub>a</sub>, S<sub>b</sub> and S<sub>c</sub>) used for the simulation was copied from the Matlab workspace to VHDL code, as well as the inputs for the targeted FPGA. The VHDL codes were simulated in ModelSim-Altera before being synthesized and implemented in FPGA. However, the stage is optional. From Matlab simulation, the designers can go the to FPGA implementation stage, without using ModelSim-Altera simulation stage. Quartus simulation environment can be used to verify the design.

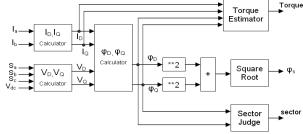

# VI. FPGA IMPLEMENTATION OF THE TORQUE AND FLUX ESTIMATORS

The algorithm of torque and flux estimation is implemented in an architecture consisting of six main blocks, as shown in Fig. 4. This architecture has six inputs: two 21-bit currents ( $I_a$  and  $I_b$ ), 12-bit high voltage DC-supply ( $V_{dc}$ ) and three switching statuses  $S_a$ ,  $S_b$  and  $S_c$ . At the end, it produces three outputs: the estimation values of torque ( $T_e$ ), flux ( $\varphi_s$ ) and sector. The sampling time chosen is 5 µs, which is limited by the ADC used.

#### A. The Architecture of Torque and Flux Estimator

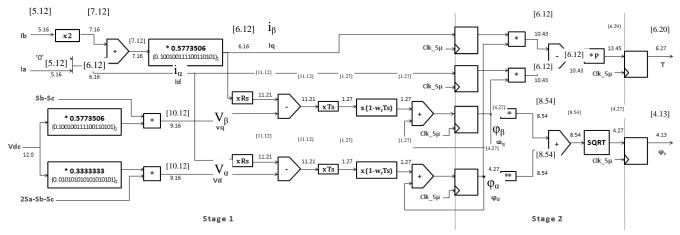

All the equations modeling the motor's behavior are implemented in a two-stage-pipelined architecture, as in Fig. 5

Fig. 3. Control structure of DTC based induction machine

# VII. FPGA IMPLEMENTATION OF THE TORQUE AND FLUX ESTIMATORS

The algorithm of torque and flux estimation is implemented in an architecture consisting of six main blocks, as shown in Fig. 4. This architecture has six inputs: two 21-bit currents ( $I_a$  and  $I_b$ ), 12-bit high voltage DC-supply ( $V_{dc}$ ) and three switching statuses  $S_a$ ,  $S_b$  and  $S_c$ . At the end, it produces three outputs: the estimation values of torque ( $T_e$ ), flux ( $\varphi_s$ ) and sector. The sampling time chosen is 5 µs, which is limited by the ADC used.

#### A. The Architecture of Torque and Flux Estimator

All the equations modeling the motor's behavior are implemented in a two-stage-pipelined architecture, as presented in Fig. 5. Several mathematical operations are performed in parallel. At the first stage, stator currents and voltages in  $\alpha\beta$ -coordinates are calculated in parallel, so that those results can be used to estimate the stator flux in the same stage. The resulted currents and flux are used to determine the flux magnitude and the torque estimation in the second stage. A 62-bit non-restoring square root is implemented in order to compute the flux magnitude.

Paper [20] has proposed that a three-stage-pipelined architecture should be implemented in this module, by separating the computation of stator currents and voltages from the estimation of the stator flux. However, the former can be considered as an immediate calculation and therefore, those calculations can be merged into a single stage. As a consequence, the latency of the estimator is reduced from 15

Fig. 4. Block Diagram of torque and flux estimators.

$\mu s$  to 10  $\mu s$ .

# B. The Digital Properties of the Torque and Flux Estimators

To achieve a good implementation, several digital properties need to be considered when designing these estimators. Adopted binary format, quantization and sampling time are amongst the key factors.

#### 1. Binary format representation

In this implementation, two's complement fixed-point representation is used during all the operations, except for the square root calculation. In that particular case, unsigned fixed-point representation is applied, since its operand and its results are always positive.

## 2. Quantization

The determination of word size (word length) is one of the critical parts in FPGA implementation. On one hand, the use of an insufficient number of bits may reduce the precision or cause a calculation error, which can unstabilize the whole system. On the other hand, the use of larger words may increase the hardware implementation area.

Fig. 5. The architecture of torque and flux estimators.

Fig. 6. Block Arithmetic unit of the  $I_{\alpha}$  and  $I_{\beta}$  calculations

#### 3. Sampling time

The sampling time Ts is limited to 5  $\mu$ s by the ADC used. Therefore, all the operations involved in this model were performed within this sampling time.

# C. The VHDL Design of the Torque and Stator Flux Estimators

The algorithm of stator flux and torque estimator is implemented in an architecture consisting of seven blocks:

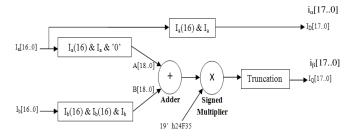

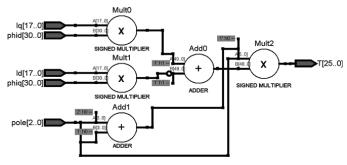

## 1. $I_{\alpha}$ and $I_{\beta}$ Calculation

The function of this block is to transform the stator currents from the motor  $I_a$  and  $I_b$  into  $\alpha$ - $\beta$  coordinates ( $I_\alpha$  and  $I_\beta$ ) refer to equation (1) and (2). In this design, the values ( $I_a$ ,  $I_b$ ) and ( $I_\alpha$ and I<sub>B</sub>) are represented on 17-bits and 18-bits two'scomplement fixed-point format [5.12 bit] and [6.12 bit] respectively to get the precise values. As shown in Fig. 5, to avoid overflow that the result calculation of " $I_a+2I_b$ " and  $\frac{1}{3}\sqrt{3}$ of the equation (2) are represented each on 19 bits, as [7.12] and [1.18] respectively. The part of  $\frac{1}{3}\sqrt{3}$  of the equation (2) is represented as 151349 (i.e.  $\frac{1}{3}\sqrt{3} \times 2^{18}$ ). In Fig. 6, the value of  $\frac{1}{3}\sqrt{3} \times 2^{18}$  is represented as "19' h24F35" (the 19 is number of bits, and the h24F35 is value of 151349 in hexadecimal). The output of the signed multiplier is represented on 38-bits, as [8.30]. However, the  $I_{\beta}$  is only represented on 18-bits as [6.12] to minimize hardware resource, so the 38-bit [8.30] is truncated to become 18-bit [6.12]. Based on the evaluation result, the 18-bit has been considered suitable to represent I<sub>B</sub> precisely. Here, the "tailor made" experience of designers is very important in order to develop the VHDL code effectively.

The efficient implementation of the algorithms largely depends on the designer's experience [33]. Therefore, the paper offers a simpler arithmetic concept based on two's complement fixed-point format for VHDL programming.

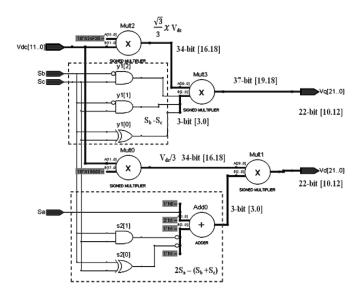

# 2. $V_{\alpha}$ and $V_{\beta}$ Calculation

The function of this block is to calculate the stator voltages in  $\alpha$ - $\beta$  components - refer to equations (4) and (5). The input is 12-bit high voltage DC-supply and three switching status. The output voltages are represented in 22-bit two's-complement fixed-point format [10.12]. The RTL viewer of the calculation is shown in Fig. 7. The numbers "19' h24F35" and "19' h15555" are to represent  $\frac{1}{3}$  and  $\frac{\sqrt{3}}{3}$  in equation (4) and (5) respectively. In these cases represent 87381 (i.e.  $\frac{1}{3}x 2^{18}$ ) and 151349 (i.e.  $\frac{\sqrt{3}}{2}x$  2<sup>18</sup>) respectively in binary 19-bits, each as [1.18]. It is important to be known that the results (before truncated) of the  $V_{\alpha}$  and  $V_{\beta}$  are allocated each to 34-bit, as [16.18], but the final values of the  $V_{\alpha}$  and  $V_{\beta}$  are only 22-bit. The most significant 9-bit and lest significant 6-bit of each the  $V_a$  and  $V_{\beta}$  34-bits are truncated, so only  $27^{th} - 6^{th}$  bits are used to represent the final values of each the  $V_{\alpha}$  and  $V_{\beta}$  as 22-bit, i.e. [10.12]. The truncations are conducted to minimize hardware resources, while still retaining sufficient precision. Once again, the tailoring and adaptation made by the designers are very important here.

## 3. $\varphi_s$ Calculation

# a. $\varphi_{\alpha}$ and $\varphi_{\beta}$ Calculation

After the calculation of  $\alpha$ - $\beta$  components of current and voltage, the  $\alpha$ - $\beta$  flux is calculated in this block (refer to equation (6) and (7)). The other input,  $R_s$ , is represented on 10-bits (5.5 bit). The output  $\alpha$ - $\beta$  components of the stator flux are represented in 31-bit two's-complement fixed-point format [4.27]. In this paper, the sampling time ( $T_s$ ) is 5  $\mu$ s. The value of  $T_s$  is represented in [1.27] as "28' h000029F" (=671), and therefore the sampling time of 5  $\mu$ s will be calculated as 4.99934  $\mu$ s (671/ $2^{27} \approx 0,00000499934$  s). Consider the ( $1-\omega_c*T_s$ ) filter part of equation (9) and (10), the part is selected: 0.999975. In this case, the value is represented in [1.22] as "23' h3FFF97" (=4194199), so 0.999974966 will be

Fig. 7. RTL viewer of the  $V_{\text{D}}$  and  $V_{\text{Q}}$  calculations

Fig. 8. RTL viewer of the magnitude calculator

Fig. 9. RTL viewer of the sector judgment

obtained to represent the 0.999975 filter. The filter is designed to overcome the problem of integration drift. Therefore, the low-pass filter is used to replace the pure integrator with appropriate cut-off frequency.

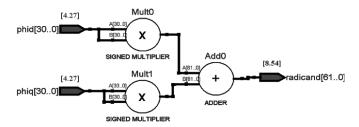

#### b. Magnitude Calculation

This block is designed to calculate the magnitude of the stator flux. The inputs of the block are the  $\alpha$ - $\beta$  components of stator flux, and the output is their magnitude, which is represented in 62 bit fixed-point format (8.54 bit). The RTL viewer for the magnitude calculation is shown in Fig. 8.

Fig. 10. RTL viewer of the Torque Calculator

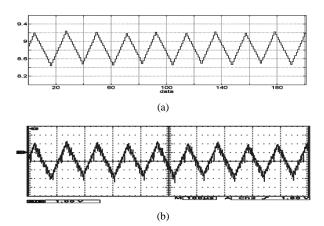

Fig. 11. The effect sampling time to torque ripple; (a) Estimated torque for Ts=50μs, (b) Estimated torque for Ts=5μs.

Fig. 12. HiL implementation of DTC

# c. Square Root Calculation

This block is design to calculate stator flux ( $\varphi_s$ ) using modified non-restoring square root algorithm. The first output of the block is represented in 31 bit fixed-point format, and then it is truncated to 17 bit (4.13 bit). The principle of the calculation is based on the powerful improved method presented in reference [34], which is created by authors originally, and can be used in general applications.

#### 4. Determination of Sector

The work has created a simpler method to judge the sector voltage vector, based on a comparison refered to in Table II, which is modified from [30]. By using Karnaugh map

simplification, it only involves two comparisons (not three comparisons). The RTL viewer of the sector judgment is shown in Fig. 9.

#### 5. Torque Calculation

The function of this block is to calculate torque - refer to equation (8). The output is represented on 55 bits [14.41] fixed-point format, and then it is truncated to 26 bits [6.20]. The RTL magnitude calculation viewer is shown in Fig. 10.

#### D. Synchronizations

In the proposed architecture of the torque and flux estimators, synchronizations are conducted in two stages. The first stage is used to synchronize the output of  $\alpha$ - $\beta$  stator currents ( $i_{\alpha}$  and  $i_{\beta}$ ) and  $\alpha$ - $\beta$  stator fluxes ( $\varphi_{\varepsilon}$  and  $\varphi_{\beta}$ ), and the second stage to synchronize the flux magnitude ( $T_{e}$ ) and the electromagnetic torque ( $\varphi_{s}$ ). It is very important to consider that the delay or un-synchrony in estimating the flux and torque, becomes the root case where the switching frequency can't be raised.

The synchronizations are designed in one cycle of the sampling time (in this case 5 µs), same with the sampling time. By using the low sampling time (high switching frequency) like this, the torque ripple can be reduced significantly. In other words, the undesired overshoot or undershoot in torque can be minimized by employing a faster sampling time. The 5 µs sampling time (in the flux and torque estimators) is only possible to be conducted/achieved by employing FPGA, and it is not possible to use microprocessors or DSPs in current condition. The one cycle synchronizations also have a function as buffer, so that the parameters can be loaded to the buffer in each clock cycle. The similar data-path and buffering concept have been introduced in [35], for application to an automatic speech recognition system based on FPGA.

# VIII. RESULTS AND DISCUSSION

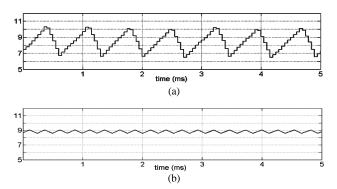

#### A. Effect of the sampling time to torque ripple

In the implementation of the DTC drive based on an FPGA, there are many digital properties which need considering, such as binary format representation (data type), quantization, sampling time and word length (size). In fact, errors or inaccuracies which are due to these digital problems can affect seriously the performance of the drive. For example, the effect of the sampling time on the torque ripple can be reduced from 2N-m to 0.2N-m by changing the sampling time from 50µs to 5µs, as shown in Fig. 11. Such digital properties have been considered in the research.

# B. Performance Analysis through Simulation and Experimental results

The experiments were conducted on Altera APEX EP20K200EFC484-2x, and consumes 2093 logic elements for the implementation. The comparisons of the area (LEs) consumption between the results of the research presented in

this paper, with other works, are shown in Table II.

TABLE II

COMPARISON OF THE LES CONSUMPTION

| No | Reference           | LEs         | DTC sampling |

|----|---------------------|-------------|--------------|

|    |                     | consumption | period (kHz) |

| 1  | Ferreira [20]       | 4,100       | 40           |

| 2  | Llor [36]           | 3,901       | 40           |

| 3  | Utsumi [37]         |             |              |

|    | - Type A controller | 3,737       | 20           |

|    | - Type B controller | 5,622       | 40           |

| 4  | Bossoufi [38]       | 3,166       | 20           |

| 5  | Proposed            | 2,093       | 200          |

As an alternative solution to the implementation, a low cost FPGA devices, such as from Cyclone family, can be used. For example Altera DE2 board which offers a rich set of features is suitable for sophisticated digital systems implementation. APEX EP20K200EFC484-2X was used for our implementation due to the availability of this device/board in our laboratory during the development of the system.

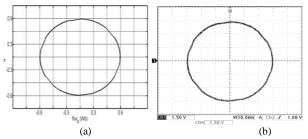

Fig. 13. The comparison between MATLAB/Simulink simulation and experimental result for torque estimation. (a) MATLAB/Simulink simulation, (b) FPGA based experimental result

Fig. 14. The comparison between MATLAB/Simulink simulation and the experimental result for flux locus. (a) MATLAB/Simulink simulation, (b) FPGA based experimental result

The tests have taken place only during certain periods of motor's steady state and the results were observed on the oscilloscope. The experiment results are based on hardwarein-the-loop (HiL). In order to evaluate these FPGA-based estimators and controller, the induction machine is simulated using the FPGA device. The induction motor is modeled based on look-up table whereby the motor currents are generated based on the switching status generated by the DTC controller and the DC link voltage. The HiL set-up is illustrated in Fig. 12 and the parameters used for the simulation and HiL are listed in Table III. Thereafter, the results were compared to the validated MATLAB/Simulink simulations (carried out in double precision). Fig. 13 and Fig. 14 show some comparison results between MATLAB/Simulink simulations and the experimental results. The conclusion is that of a fairly good match, It is important to know that the experimental outputs are displayed through a 12-bit DAC. So, all outputs are truncated within 12-bits. Therefore, it is fair to accept that the outputs are not perfectly the same as the simulation outputs. However, the results have proved that the proposed FPGA implementation of the torque and stator flux estimators was successful. This means that the main problem - "the heart of the DTC" of the FPGA implementation - has been resolved. All units in the system have been designed in fully generic VHDL code, independent of the target implementation technology, without the need for third party products or special FPGAs. Given that most of the DTC research solutions have limitations on the performance of the implementation of the torque and flux estimator, obviously this contribution has been eagerly awaited by researchers to support, enable and take forward their DTC improvements.

#### IX. CONCLUSIONS

This paper has achieved the reduction of the sampling time (to increase the sampling frequency) by using FPGAs, so that the appropriate value of the band width of the hysteresis comparator can be achieved. The technique will retain the simple control structures of the DTC drive. The paper presented an effective way to design, simulate and implement hysteresis-based DTC utilizing FPGAs. All modules in the system have been designed in fully generic VHDL code, which is independent of the FPGA target implementation technology. All calculations in the modules are conducted in two's complement fixed-point arithmetic with appropriate word sizes. The choice of word sizes, the binary format and the sampling time used are very important in order to achieve a good implementation of the estimators. To get simpler implementation and fast computation, several methods were introduced: i) the backward Euler approach to calculate the discrete integration operation of stator flux, ii) the modified non-restoring method to calculate complicated square root operation of stator flux, iii) a new sector analysis method; the simulation results of the DTC model in MATLAB/Simulink,

TABLE III

INDUCTION MACHINE PARAMETERS

| Parameters                             | Type or values           |  |

|----------------------------------------|--------------------------|--|

| Rotor type                             | Squirrel-cage            |  |

| Nominal power                          | 2425 VA                  |  |

| Voltage (line to line)                 | 400 V                    |  |

| Frequency                              | 50 Hz                    |  |

| Stator resistance, R <sub>s</sub>      | 5.5 ohm                  |  |

| Rotor resistance, R <sub>r</sub>       | 4.45 ohm                 |  |

| Stator self inductance, L <sub>s</sub> | 0.0149 H                 |  |

| Rotor self inductance, Lr              | 0.0149 H                 |  |

| Mutual inductance, L <sub>m</sub>      | 0.299 H                  |  |

| Combined inertia, J                    | $0.00925 \text{ kg-m}^2$ |  |

| Combined viscous friction, B           | 0.006 N.m.s              |  |

| Number of pole pairs, P                | 2                        |  |

which performed double-precision calculations, are used as references to digital computations executed in FPGA implementation. The Hardware-in-the-loop (HIL) method is used to verify the minimal error between MATLAB/Simulink simulation and the experimental results. The design, which was coded in synthesizable VHDL code for implementation on Altera APEX20K200EFC484-2x device, has produced very good estimations, giving minimal errors when being compared to MATLAB/Simulink double-precision calculations.

#### ACKNOWLEDGMENT

The authors would like to thank the Universiti Teknologi Malaysia (UTM) for providing the funding for this research.

#### REFERENCES

- I. Takahashi and T. Noguchi, "A New Quick-Response and High-Efficiency Control Strategy of an Induction Motor," *IEEE Transactions* on *Industry Applications*, vol. Vol.IA-22, No.5, pp. 820-827, Sept/Oct 1986

- [2] A. Jidin, et al., "Torque ripple minimization in DTC induction motor drive using constant frequency torque controller," in Electrical Machines and Systems (ICEMS), 2010 International Conference on, 2010, pp. 919-924.

- [3] N. R. N. Idris and A. H. M. Yatim, "Direct torque control of induction machines with constant switching frequency and reduced torque ripple," *Industrial Electronics, IEEE Transactions on*, vol. 51, pp. 758-767, 2004.

- [4] A. Tripathi, et al., "Torque ripple analysis and dynamic performance of a space vector modulation based control method for AC-drives," Power Electronics, IEEE Transactions on, vol. 20, pp. 485-492, 2005.

- [5] D. Casadei, et al., "Implementation of a direct control algorithm for induction motors based on discrete space vector modulation," Power Electronics, IEEE Transactions on, vol. 15, pp. 769-777, 2000.

- [6] C. Lascu, et al., "A modified direct torque control for induction motor sensorless drive," *Industry Applications, IEEE Transactions on*, vol. 36, pp. 122-130, 2000.

- [7] T. G. Habetler, et al., "Direct torque control of induction machines using space vector modulation," *Industry Applications*, *IEEE Transactions on*, vol. 28, pp. 1045-1053, 1992.

- [8] T. Noguchi, et al., "Enlarging switching frequency in direct torquecontrolled inverter by means of dithering," *Industry Applications, IEEE Transactions on*, vol. 35, pp. 1358-1366, 1999.

- [9] J. Beerten, et al., "Predictive Direct Torque Control for Flux and Torque Ripple Reduction," Industrial Electronics, IEEE Transactions on, vol. 57, pp. 404-412.

- [10] J. Kley, et al., "Performance evaluation of model predictive direct torque control," in Power Electronics Specialists Conference, 2008. PESC 2008. IEEE, 2008, pp. 4737-4744.

- [11] G. Papafotiou, et al., "Model Predictive Direct Torque Control—Part II: Implementation and Experimental Evaluation," Industrial Electronics, IEEE Transactions on, vol. 56, pp. 1906-1915, 2009.

- T. Geyer, et al., "Model Predictive Direct Torque Control—Part

I: Concept, Algorithm, and Analysis," Industrial Electronics, IEEE Transactions on, vol. 56, pp. 1894-1905, 2009.

- [13] B. K. Bose and P. M. Szczesny, "A microcomputer-based control and simulation of an advanced IPM synchronous machine drive system for electric vehicle propulsion," *Industrial Electronics, IEEE Transactions* on, vol. 35, pp. 547-559, 1988.

- [14] L. Lianbing, et al., "A high-performance direct torque control based on DSP in permanent magnet synchronous motor drive," in *Intelligent Control and Automation*, 2002. Proceedings of the 4th World Congress on, 2002, pp. 1622-1625 vol.2.

- [15] S. M. A. Cruz, et al., "DSP implementation of the multiple reference frames theory for the diagnosis of stator faults in a DTC induction motor drive," Energy Conversion, IEEE Transactions on, vol. 20, pp. 329-335, 2005.

- [16] A. Jidin, et al., "Simple Dynamic Overmodulation Strategy for Fast Torque Control in DTC of Induction Machines with Constant Switching Frequency Controller," in *Industry Applications Society Annual Meeting (IAS)*, 2010 IEEE, 2010, pp. 1-8.

- [17] N. R. N. Idris, et al., "A New Torque and Flux Controller for Direct Torque Control of Induction Machines," *Industry Applications, IEEE Transactions on*, vol. 42, pp. 1358-1366, 2006.

- [18] A. Jidin, et al., "An Optimized Switching Strategy for Quick Dynamic Torque Control in DTC-Hysteresis-Based Induction Machines," Industrial Electronics, IEEE Transactions on, vol. 58, pp. 3391-3400, 2011.

- [19] E. Monmasson and M. N. Cirstea, "FPGA Design Methodology for Industrial Control Systems: A Review," *Industrial Electronics, IEEE Transactions on*, vol. 54, pp. 1824-1842, 2007.

- [20] S. Ferreira, et al., "Design and prototyping of direct torque control of induction motors in FPGAs," in *Integrated Circuits and Systems Design*, 2003. SBCCI 2003. Proceedings. 16th Symposium on, 2003, pp. 105-110.

- [21] J. W. Kang and S. K. Sul, "Analysis and prediction of inverter switching frequency in direct torque control of induction machine

- based on hysteresis bands and machine parameters," *Industrial Electronics, IEEE Transactions on*, vol. 48, pp. 545-553, 2001.

- [22] A. Jidin, et al., "Extending switching frequency for torque ripple reduction utilizing a constant frequency torque controller in dtc of induction motors," *Journal of Power Electronics*, vol. 11, pp. 148-155, 2011.

- [23] R. K. Behera and S. P. Das, "High performance induction motor drive: A dither injection technique," in *Energy, Automation, and Signal (ICEAS)*, 2011 International Conference on, 2011, pp. 1-6.

- [24] N. R. N. Idris and A. H. M. Yatim, "Reduced torque ripple and constant torque switching frequency strategy for direct torque control of induction machine," in *Applied Power Electronics Conference and Exposition*, 2000. APEC 2000. Fifteenth Annual IEEE, 2000, pp. 154-161 vol.1.

- [25] A. Saleem, et al., "Hardware-In-the-Loop for on-line identification and control of three-phase squirrel cage induction motors," Simulation Modelling Practice and Theory, vol. 18, pp. 277-290, 2010.

- [26] A. Barakat, et al., "Analysis of synchronous machine modeling for simulation and industrial applications," Simulation Modelling Practice and Theory, vol. 18, pp. 1382-1396, 2010.

- [27] N. R. N. Idris and A. H. M. Yatim, "An improved stator flux estimation in steady state operation for direct torque control of induction machines," in *Industry Applications Conference*, 2000. Conference Record of the 2000 IEEE, 2000, pp. 1353-1359 vol.3.

- [28] N. R. N. Idris and A. H. M. Yatim, "An improved stator flux estimation in steady-state operation for direct torque control of induction machines," *Industry Applications, IEEE Transactions on*, vol. 38, pp. 110-116, 2002.

- [29] S. Samavi, et al., "Modular array structure for non-restoring square root circuit," *Journal of Systems Architecture*, vol. 54, pp. 957-966, 2008.

- [30] T. Sutikno, et al., "New approach FPGA-based implementation of discontinuous SVPWM," Turk J Elec Eng & Comp Sci, vol. 18, p. 6, 2010.

- [31] C. T. Kowalski, et al., "FPGA Implementation of DTC Control Method for the Induction Motor Drive," presented at the EUROCON, 2007. The International Conference on Computer as a Tool, 2007.

- [32] E. Monmasson, et al., "FPGAs in Industrial Control Applications," Industrial Informatics, IEEE Transactions on, vol. 7, pp. 224-243, 2011

- [33] J. J. Rodriguez-Andina, et al., "Features, Design Tools, and Application Domains of FPGAs," *Industrial Electronics, IEEE Transactions on*, vol. 54, pp. 1810-1823, 2007.

- [34] T. Sutikno, et al., "A simple strategy to solve complicated square root problem in DTC for FPGA implementation," in *Industrial Electronics* & Applications (ISIEA), 2010 IEEE Symposium on, 2010, pp. 691-695.

- [35] O. Cheng, et al., "Hardware–Software Codesign of Automatic Speech Recognition System for Embedded Real-Time Applications," *Industrial Electronics, IEEE Transactions on* vol. 58, pp. 850-859, March 2011

- [36] A. Llor, et al., "Comparison of DTC implementations for synchronous machines," in Power Electronics Specialists Conference, 2004. PESC 04. 2004 IEEE 35th Annual, 2004, pp. 3581-3587 Vol.5.

- [37] Y. Utsumi, et al., "Comparison of FPGA-based Direct Torque Controllers for Permanent Magnet Synchronous Motors," *Journal of Power Electronics*, vol. 6, pp. 114-120, 2006.

- [38] B. Bossoufi, et al., "FPGA-based implementation by direct torque control of a PMSM machine," in Compatibility and Power Electronics (CPE), 2011 7th International Conference-Workshop, 2011, pp. 464-469.